# RECENT ADVANCES IN EMBEDDED SYSTEM

Akshatha K Puneet Kalia

## RECENT ADVANCES IN EMBEDDED SYSTEM

# RECENT ADVANCES IN EMBEDDED SYSTEM

Akshatha K

Puneet Kalia

## Published by: Alexis Press, LLC, Jersey City, USA www.alexispress.us

#### © RESERVED

This book contains information obtained from highly regarded resources.

Copyright for individual contents remains with the authors.

A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereinafter invented, including photocopying, microfilming and recording, or any information storage or retrieval system, without permission from the publishers.

For permission to photocopy or use material electronically from this work please access alexispress.us

### First Published 2022

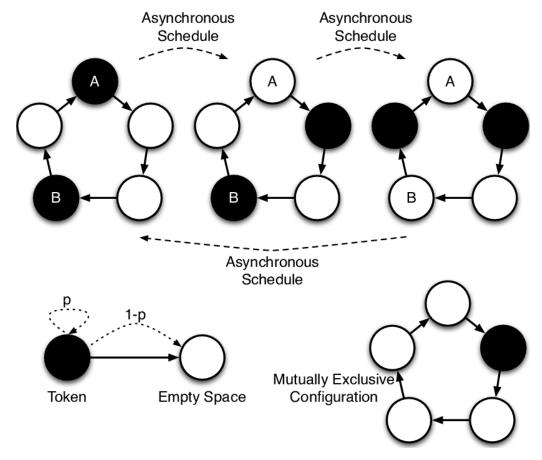

A catalogue record for this publication is available from the British Library

Library of Congress Cataloguing in Publication Data

Includes bibliographical references and index.

Recent Advances in Embedded System by Akshatha K, Puneet Kalia

ISBN 978-1-64532-871-1

## **CONTENTS**

| <b>Chapter 1.</b> An Introduction to Embedded System                          | 1     |

|-------------------------------------------------------------------------------|-------|

| <b>Chapter 2.</b> A Comprehensive study on Continuous Dynamics                | 14    |

| Chapter 3. Discrete Dynamics of Complex Systems                               | 26    |

| Chapter 4. The Hybrid Intelligent Systems                                     | 37    |

| Chapter 5. Composition of state machines — Mrs. Kehkeshan Jalall S            | 47    |

| Chapter 6. Hardware Verification Using a Simulator                            | 62    |

| Chapter 7. Composition of State Machines — Mrs. Manaswini R                   | 72    |

| Chapter 8. Concurrent Models of Computation                                   | 81    |

| Chapter 9. An Extensive Study on Sensors and Actuators                        | 90    |

| Chapter 10. Embedded Sensor Based Systems                                     | 99    |

| Chapter 11. The Memory Architecture Assignment Schemes                        | . 108 |

| Chapter 12. A Comparison between Input and Output Type Hardware               | . 122 |

| Chapter 13. Multitasking Process and Message Passing                          | . 131 |

| Chapter 14. Scheduling Network Based Method and Mutual Exclusion              | . 139 |

| Chapter 15. A Systematic Approach to Reachability Analysis and Model Checking | . 148 |

| Chapter 16. Personalized Quantitives Analysis Recommendation                  | . 156 |

| Chapter 17. The Implicit Function on Invariants and Temporal Logic Technique  | . 165 |

| Chapter 18. Simplified Determination Algorithm on Execution Time Analysis     | . 173 |

| Chapter 19. 19 Optimization Technique for Equivalence and Refinement          | . 180 |

| Chapter 20. Advance Optimization in Power and Energy Analysis        | 188 |

|----------------------------------------------------------------------|-----|

| Chapter 21. Sequential Software In A Concurrent World                | 196 |

| Chapter 22. Reachability Analysis and Model Checking                 | 204 |

| Chapter 23. The Analog/Digital Interface — Prof. Sudhir Kumar Sharma | 213 |

## CHAPTER 1

## AN INTRODUCTION TO EMBEDDED SYSTEM

Ms. Akshatha K. Assistant Professor Department of Electronics and Communication Engineering, Presidency University, Bangalore, India Email Id- akshatha.k@presidencyuniversity.in

## **ABSTRACT:**

An embedded system is a computer system that is designed to perform specific functions within a larger system. It typically consists of a microcontroller or microprocessor, memory, and other components that are integrated into a single device. Embedded systems are commonly found in a wide range of applications, including automotive, medical devices, consumer electronics, and industrial automation. Embedded systems is their ability to operate in real-time, meaning that they can respond to events and inputs in a timely and predictable manner. This is often accomplished through the use of specialized software and hardware components that are designed to handle specific tasks.

## **KEYWORDS:**

Automation Consumer Electronics, Embedded System, Medical Device, microprocessor.

## INTRODUCTION

Embedded systems are all around us, from the tiny microcontrollers powering our home appliances to the sophisticated control systems used in spacecraft. An embedded system is a combination of hardware and software designed to perform a specific function within a larger system. These systems are often designed to operate autonomously or with minimal human intervention and can be found in a wide variety of applications, from consumer electronics to medical devices to industrial automation.

The term "embedded" refers to the fact that the system is integrated into a larger device or system, and is typically not visible to the end-user. Embedded systems are often highly specialized, tailored to specific applications and optimized for performance, power consumption, and cost. They are designed to interact with the physical world and often include sensors, actuators, and other peripherals that allow them to interact with their environment. Embedded systems have been around for decades, but their importance has grown exponentially in recent years with the rise of the Internet of Things (IoT) and the proliferation of connected devices. As more and more devices become connected to the internet, the need for small, efficient, and powerful embedded systems has become more critical than ever[1], [2].

One of the defining characteristics of embedded systems is their real-time nature. Real-time systems are designed to respond to events as they happen, often in fractions of a second. This requires specialized hardware and software that can respond quickly and accurately to external stimuli. Real-time embedded systems are used in a wide variety of applications, from controlling the timing and synchronization of industrial machinery to managing the safety-critical functions of medical devices. Another important aspect of embedded systems is their low power consumption. Many embedded systems are battery-powered or otherwise limited in terms of power supply, which means that they must be designed to operate efficiently and conserve power whenever possible. This requires careful consideration of the hardware and software components of the system, as well as optimization of power management features[3], [4].

Embedded systems are typically designed by multidisciplinary teams of engineers, including hardware designers, software developers, and system architects. The design process can be complex and challenging, as it requires consideration of a wide range of factors, including performance, power consumption, cost, reliability, and security. Embedded system designers must also be familiar with a range of programming languages and software development tools, as well as hardware design techniques and principles. One of the key challenges facing embedded system designers is the need to balance the conflicting requirements of performance and power consumption. As devices become more sophisticated and powerful, the demand for increased performance has grown, but this must be balanced against the need to conserve power and extend battery life. This requires careful consideration of the hardware and software components of the system, as well as the algorithms and data structures used to implement the system's functionality[5], [6].

Another important consideration for embedded systems is security. As more and more devices become connected to the internet, the need for secure and reliable systems has become more critical than ever. Embedded systems are particularly vulnerable to attacks, as they often have limited resources and are designed to operate in challenging environments. Designers must take a range of security measures into consideration, including encryption, authentication, and access control, to ensure that their systems are protected against cyber threats.

Embedded systems are an integral part of our modern world and are critical to the functioning of many devices and systems. As devices become more connected and sophisticated, the demand for small, efficient, and powerful embedded systems has grown, and the importance of these systems is only set to increase in the years to come. Embedded system designers face a range of challenges, from balancing performance and power consumption to ensuring the security and reliability of their systems, but the rewards of developing successful embedded systems are significant, as they can have a significant impact on the way we live and work.

Embedded systems are used in a wide range of industries and applications. Some of the most common applications include consumer electronics, automotive systems, medical devices, industrial automation, and aerospace and defense. In consumer electronics, embedded systems are used in devices such as smartphones, smart home appliances, and gaming consoles. These systems are designed to provide fast, reliable, and intuitive user experiences while also conserving power and extending battery life.

In automotive systems, embedded systems are used in everything from engine management and control to safety-critical functions such as anti-lock brakes and airbag deployment. These systems must be designed to operate in harsh environments and withstand shocks, vibrations, and extreme temperatures. They must also be highly reliable and operate in real-time to respond to changing road and traffic conditions.

For embedded systems to be effective and durable, low-power hardware and software design is essential. In order to evaluate the energy performance of software and hardware, accurate energy consumption measurement is essential. This measurement also offers design insights that may be used to create new paradigms for algorithm or code optimization in terms of energy efficiency and system cost. There is some literature that has studied this subject area, but it lacks in-depth comparisons and analysis. We first demonstrate in this study the importance of precise energy consumption analysis for embedded systems. The main approaches for evaluating the energy use of embedded systems that have been studied in the literature may be divided into three categories: measurement-based energy profiling, model-based energy estimation, and simulatorbased energy estimation. On the basis of these techniques' qualities, several subgroups are further created.

A crucial component of engineering education is offering students the opportunity to use what they learn in the classroom and to be exposed to real-world issues while they are still in school. One of the key courses that ties theoretical electrical engineering education to the actual world is the Embedded Systems course at Princess Sumaya University for Technology (PSUT). The use of project-based learning to improve the teaching of the Embedded Systems course at PSUT is described in this study. The comments from students demonstrated the method's success in improving students' comprehension and capacity for using embedded systems design ideas to address actual engineering challenges.

Many applications, including those for home automation, automobile systems, air surveillance, and, more recently, IoT subnets, typically use distributed embedded systems (Internet of things). Due to the variety of hardware and software as well as the differences in message flows that should occur based on protocol use and application flow requirements, distributed embedded systems are highly complicated. Hardware, software, and the technology used to connect the different embedded systems all need to be tested for the distributed embedded systems. Numerous devices, tools, techniques, and procedures are needed to test distributed embedded systems. It is difficult to test the communication that takes place between the various embedded systems. Comprehensive testing requires the continuous availability of the complete distributed embedded system, which cannot be guaranteed, as well as the testing system.

An agricultural nation's growth depends heavily on agriculture. Because the monsoon is unpredictable, unequal water is a significant issue all year long. All of this results in poor productivity and inadequate output. By increasing the effectiveness of agricultural technology, the agricultural sector's scientific approach will result in a fundamental shift in crop production. The architecture of practically all sectors has been altered by the Internet of Things (IoT), the quickening growth of technology, from statistics to quantitative approaches, and smart agriculture. This radical transformation, intended to upend the conventional wisdom, has brought up a number of difficulties as well as fresh possibilities. IoT and embedded system (ES) development and embedded sensors in the smart agricultural sector monitoring are offered as the basis for smart agriculture design.

Evaluation, group physical education, and data from a product's decision-making process may be used to compare the off-the-shelf standard. The use of Genetic Algorithm in actual education and preparation assistance for augmented reality and computer-generated reality. The application model of Virtual Reality (VR) innovation in this sector is created using real education and preparation. Highlights of VR innovation, for example, discernment, presence, intellect, selfcontrol, and so forth, may be widely used in real education, and preparation plays a key role. All contemporary electronic components have embedded systems as a necessary component. In addition to being the foundation of the Internet, embedded systems, very specialized vertical markets, and Internet of Things solutions are employed in many network installations and network applications. Devices that are embedded are made to construct certain computer systems.

Evaluation, group physical education, and data from a product's decision-making process may be used to compare the off-the-shelf standard. The use of Genetic Algorithm in actual education and

preparation assistance for augmented reality and computer-generated reality. The application model of Virtual Reality (VR) innovation in this sector is created using real education and preparation. Highlights of VR innovation, for example, discernment, presence, intellect, selfcontrol, and so forth, may be widely used in real education, and preparation plays a key role. All contemporary electronic components have embedded systems as a necessary component. In addition to being the foundation of the Internet, embedded systems, very specialised vertical markets, and Internet of Things solutions are employed in many network installations and network applications. Devices that are embedded are made to construct certain computer systems.

In order to engage and excite their pupils in the classroom, educators have joined a wider variety of non-specialists in the creation (design and development) of embedded systems. Because of this variety and the complexity of current embedded systems development platforms, there are prohibitive hurdles to entry. The rationale, specifications, implementation, and assessment of a novel programming platform that allows even inexperienced users to produce effective and efficient software for embedded devices are presented in this work. The platform consists of two main parts: CODAL, an effective component-oriented C++ runtime for microcontrollers, and Microsoft MakeCode, a web application that encompasses an accessible IDE for microcontrollers. We demonstrate how MakeCode and CODAL work together to provide an installation-free, cross-platform, high level programming experience for embedded devices without compromising performance or effectiveness.

Every digital device's central processing unit is called an embedded system. Understanding the embedded system is essential for the design and development of new digital devices and systems. Learning embedded systems in the context of engineering education is still difficult for millennials. Due to the fact that it requires the use of mathematics, programming, and practical understanding of the electronic and electrical components based in it. For new-generation learners to meet their need for understanding of embedded systems, traditional teaching technique has become less effective. As a result, new technical tools and methods must be included into the instructional methods. A new technology in the area of engineering education is augmented reality (AR). This technology has proliferated in the educational sector to simplify difficult topics via the use of computer-generated 3D data, animation, visual effects, and immersion. An augmented reality-based approach for teaching embedded systems to engineering students is presented in this research. To provide students with an AR learning experience, the suggested framework makes use of a physical user interface made up of AR markers, a USB camera, a display device, and the processing unit. The engineering education faculty examined the newly designed system's usefulness[7], [8].

## DISCUSSION

Medical devices are another important application area for embedded systems. These systems are used in everything from pacemakers and insulin pumps to diagnostic equipment and surgical robots. They must be designed to operate safely and reliably in a wide range of environments, from hospitals to patients' homes. They must also be highly secure to protect patient data and prevent unauthorized access. In industrial automation, embedded systems are used in everything from factory automation to building control systems. These systems must be designed to operate in real-time and respond to changing conditions quickly and accurately. They must also be highly reliable and operate in harsh environments, with temperature extremes, dust, and humidity.

In aerospace and defense, embedded systems are used in everything from avionics and spacecraft control systems to missile guidance and navigation. These systems must be designed to operate in extreme environments, from the vacuum of space to high-temperature and high-pressure environments. They must also be highly secure to prevent unauthorized access and ensure the safety of personnel and equipment. The development of embedded systems is a complex process that requires a range of specialized skills and knowledge. The process typically begins with the identification of requirements, which are used to define the system's functionality and performance characteristics. This is followed by the design phase, where the system's hardware and software components are developed and integrated.

The design phase typically involves a range of tools and techniques, including computer-aided design (CAD), simulation, and modeling. These tools allow designers to develop and test different components of the system before they are integrated into the final product. Once the system's hardware and software components have been developed, they must be integrated and tested. This involves the use of specialized test equipment and techniques to ensure that the system meets its performance and reliability requirements. Testing is typically performed in a range of environments, from the lab to the field, to ensure that the system operates correctly under a wide range of conditions.

Once the system has been developed and tested, it must be deployed and maintained. This involves the installation of the system in its final environment and the provision of ongoing support and maintenance. This may include the provision of software updates, hardware repairs, and other maintenance activities to ensure that the system continues to operate correctly over its lifetime. One of the key challenges facing embedded system designers is the need to balance the conflicting requirements of performance and power consumption. As devices become more sophisticated and powerful, the demand for increased performance has grown, but this must be balanced against the need to conserve power and extend battery life. This requires careful consideration of the hardware and software components of the system, as well as the algorithms and data structures used to implement the system's functionality.

Another important consideration for embedded systems is security. As more and more devices become connected to the internet, the need for secure and reliable systems has become more critical than ever. Embedded systems are particularly vulnerable to attacks, as they often have limited resources and are designed to operate in challenging environments. Designers must take a range of security measures into consideration, including encryption, authentication, and access control, to ensure that their systems are protected. A cyber-physical system (CPS) combines computer with physical processes, and the behaviour of the system is determined by both its cyber and physical components. Physical processes are monitored and controlled by embedded computers and networks, often via feedback loops where calculations are affected by physical processes and vice versa.

Thus, CPS is about the meeting of the physical and the digital, not their unification. Separate understanding of the computational and physical components is insufficient. Instead, we must comprehend how they interact we describe the engineering concepts of such systems and the procedures by which they are created using a few CPS examples. The information technology (IT) revolution of the 20th century may be surpassed by CPS applications. Take a look at the

following instances[7], [9]. The heart must often be stopped during cardiac surgery in order to be operated on, and it must afterwards be restarted. Such a procedure is quite dangerous and has a lot of negative side effects. In place of stopping the heart, a surgeon might do surgery on a beating heart, according to a number of study teams. This is made feasible by two essential notions. First, surgical instruments may be robotically controlled to move in sync with heartbeat. Therefore, while the heart is still beating, a surgeon may use a gadget to continuously apply pressure to a specific place on the heart. Additionally, a stereoscopic video system may give the surgeon the illusion of a motionless heart via video (Rice, 2008). Although the heart is still beating, it seems to the surgeon that the heart has stopped. It takes comprehensive modelling of the heart, the equipment, the computer gear, and the software to produce such a surgical system. Software must be carefully designed to provide accurate timing and secure fallback procedures to manage errors. Additionally, in order to guarantee high confidence, a thorough investigation of the models and designs is required.

Instance 1.2 Imagine a city where automobiles and traffic lights work together to maintain a smooth flow of traffic. Imagine, for example, that you would never have to stop at a red light unless there was genuine traffic. A costly infrastructure that can identify automobiles on the road may be used to implement such a system. However, it could be preferable to have the automobiles themselves collaborate. They coordinate the usage of common resources, such as junctions, by keeping track of their location and communicating. Naturally, the feasibility of such a system depends on its reliability. Failures could have devastating results.

A well-designed flight control system may stop certain reasons of a crash even if it is impossible to stop all potential causes. These systems are effective illustrations of cyber-physical systems. In conventional aircraft, the pilot steers the craft using mechanical and hydraulic connections between cockpit controls and moveable surfaces on the wings and tail. In a fly-by-wire aircraft, the flight computer relays the pilot's directions to actuators in the wings and tail through an electrical network. Fly-by-wire aeroplanes use less fuel since they are lighter than conventional aircraft. Additionally, they have shown to be more dependable[10]. Since a computer mediates the pilot's orders in a fly-by-wire aircraft, the computer may alter the pilot's commands. Many contemporary flight control systems alter pilot instructions under certain conditions. For instance, Airbus commercial aircraft utilise a method called flight envelope protection to stop an aircraft from straying outside of its safe operating range. For instance, they may stop a pilot from initiating a stall.

The idea of flying envelope protection may be expanded to assist avoid certain more accident causes. For instance, if implemented, Lee (2001)'s soft walls system would follow the position of the aircraft on which it is mounted and keep it from flying into terrain features like mountains and structures. In Lee's idea, the fly-by-wire flight control system generates a virtual pushing force that pushes the aeroplane away when it approaches the border of an obstacle. The pilot has a soft wall feeling that causes the plane to deviate.

The development and deployment of such a system faces several difficulties, both technological and non-technical. For a discussion of some of these concerns. Although the soft walls system from the preceding example seems somewhat far-fetched, there are more practical variations that have been implemented or are in advanced phases of research and development in the field of automobile safety. For instance, many modern vehicles alert the driver when lane changes are made accidentally. Think about the considerably harder issue of automatically changing the driver's behaviour. Clearly, this is more difficult than just alerting the motorist.

How can you be certain that the system will respond and take control only when necessary and in the precise amount that intervention is required? Numerous more uses come to mind, including those that help the elderly, enable telesurgery, which enables a surgeon to do an operation from a distance, and enable household appliances to work together to reduce the load on the power grid. Furthermore, it is simple to imagine how CPS could be used to enhance a variety of current systems, including robotic manufacturing systems, electric power generation and distribution, process control in chemical factories, distributed computer games, the transportation of manufactured goods, building heating, cooling, and lighting systems, elevators, and bridges that keep track of their own health. Such advancements have the potential to have a huge influence on economics, energy consumption, and safety.

Numerous of the aforementioned examples will be implemented using a framework similar to the one. This drawing is divided into three major sections. The "physical" component of a cyberphysical system is firstly the physical plant. Simply expressed, it refers to the component of the system that cannot be implemented using computers or digital networks. Mechanical components, biological or chemical processes, or human operators may all be a part of it. The second is one or more computational platforms, which may include one or more processors, actuators, operating systems, and sensors. A network fabric, which offers the means for the computers to interact, is the third component. The platforms and network fabric work together to create the "cyber" component of the cyber-physical system.

Data produced by the sensors via the physical plant is impacted by the actions done by the actuators. Actuator 1 on Platform 2 in the picture directs the physical plant. Sensor 2 is used to measure the physical plant's processes. The Computation 2 box implements a control rule that decides what instructions to provide the actuator depending on sensor data. A feedback control loop is the name given to such a loop. Platform 1 uses Sensor 1 to take further measurements and communicates with Platform 2 over the network fabric. A new control rule is realised in Computation 3 and combined with Computation 2's, perhaps preempting it.

When using a print-on-demand service, think about a high-speed printing press. This might have a similar organisational structure but with a lot more platforms, sensors, and actuators. The motors that press paper and apply ink on it may be controlled by the actuators. The regulations may provide a plan of action. At the US National Science Foundation in 2006, Helen Gill invented the phrase "cyber-physical systems." Although we may be inclined to equate the word "cyberspace" with CPS, its origins are earlier and deeper. Instead of seeing them as having descended from one another, it would be more correct to see the phrases "cyberspace" and "cyber-physical systems" as coming from the same root, "cybernetics."

Norbert Wiener (Wiener, 1948), an American mathematician who had a significant influence on the development of control systems theory, is credited with coining the term "cybernetics." Wiener invented the system that allowed anti-aircraft weapons to automatically aim and fire during World War II. Although he did not utilise digital computers, the techniques he used share many of the same concepts as the vast majority of computer-based feedback control systems in use today. According to Wiener, the word comes from the Greek letter "v" (kybernetes), which might refer to a helmsman, governor, pilot, or rudder.

The analogy applies well to control systems. Control and communication are combined in cybernetics, according to Wiener. His conception of control was firmly based on closed-loop feedback, in which measurements of physical processes drive the control logic, which in turn drives the physical processes. The combination of physical processes, calculation, and communication is known as cybernetics, even though Wiener did not employ digital computers; instead, control logic functions as a computation. Wiener was unable to foresee the significant impacts of digital networks and computing. The immense influence that CPS will have is further shown by the fact that the term "cyber-physical systems" is ambiguously defined as the combination of cyberspace with physical processes. CPS uses information technology that is significantly superior to even the most optimistic predictions made in Wiener's day.

Internet of Things (IoT), Industry 4.0, the Industrial Internet, Machine-to-Machine (M2M), the Internet of Everything, TSensors (trillion sensors), and the Fog are all phrases that are now in vogue (like the Cloud, but closer to the ground). All of them illustrate a technology that profoundly links our physical and digital worlds. Since the word CPS does not specifically relate to either implementation strategies (such as the "Internet" in IoT) or specific applications (such as the "Industry" in Industry 4.0), we believe it to be more enduring and fundamental than any of the others. Instead, it concentrates on the basic philosophical conundrum of combining the physical and cybernetic engineering traditions depending on the kind of paper, the temperature, and the humidity for adjusting for paper stretch. In the event of a paper jam, a networked system similar may be utilized to trigger a quick shutdown in order to protect the equipment. To avoid calamities, such shutdowns must be carefully planned throughout the whole system. High-end instrumentation systems and the generation and distribution of energy experience comparable circumstances.

We provide a compelling example of a cyber-physical system in this section. The purpose of this example is to highlight the significance of the wide range of subjects discussed in this literature. The particular application is the Stanford Testbed of Autonomous Rotorcraft for Multi Agent Control (STARMAC), created in collaboration between Stanford and Berkeley by Claire Tomlin and colleagues (Hoffmann et al., 2004). The STARMAC, a tiny quadrotor aircraft, in flight. Its main objective is to act as a testbed for 6 Introduction to Embedded Systems, Lee & Seshia working with methods for multi-vehicle autonomous control. The goal is to enable multi-vehicle cooperation for a shared job.

The creation of such a system is fraught with difficulties. The first is that driving the car is not easy. The four rotors, which provide a changeable amount of downward force, are the major actuators. The vehicle's four rotors' propulsion may be balanced to allow it to take off, land, spin, and even flip in the air. How do we decide how much thrust to use? The vehicle's weight is another important factor. It naturally becomes heavier as it gets heavier because it has to transport more stored energy. It requires more force to fly the heavier it is, which calls for larger and more powerful motors and rotors. When the car is so hefty that the rotors endanger people, the design has crossed a critical barrier. Safety is a major issue, even with a very small vehicle, hence the system must be developed with fault management.

Thirdly, the vehicle must function in a context and engage with its surroundings. It may, for instance, be continuously run by a vigilant person using a remote control. Or, it may be anticipated to function autonomously, to take off, do a task, go back, and land.

The Design Processing is not able to profit from the alert human's observation. Greater sensor sophistication is necessary for autonomous operation. The vehicle must do localisation in order to maintain track of its whereabouts. It must be able to detect obstructions and recognise the location of the ground. Such vehicles may even be able to land on a ship's pitching deck by themselves with appropriate design. Additionally, the vehicle must constantly check its own performance in order to identify problems and respond appropriately in order to minimise damage. It is simple to envision several alternative applications that have characteristics in common with the quadrotor challenge. Operating on a beating heart is analogous to the challenge of landing a quadrotor craft on a tossing ship. It needs a thorough knowledge of the interplay between the dynamics of the embedded system the quadrotor, the robot, and the dynamics of the environment the ship, the heart.

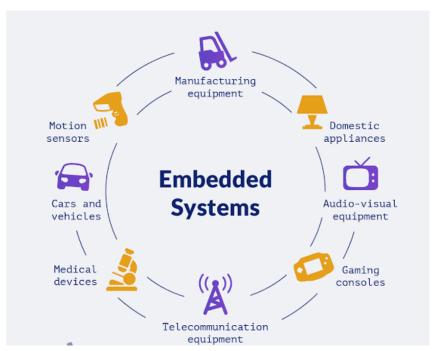

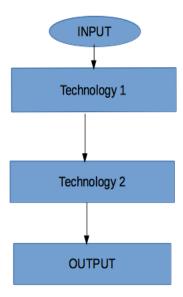

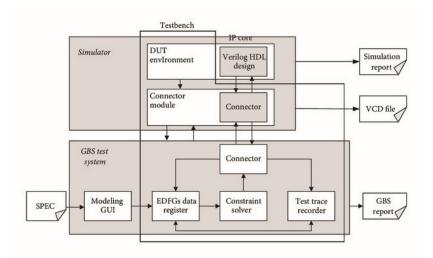

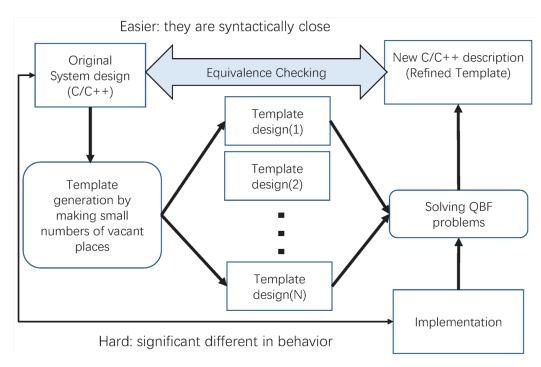

Using the quadrotor example to show how the different pieces contribute to the design of such a system, the remainder of this chapter will describe the various components of this book. Understanding how to build and execute cyber-physical systems is the aim of this book. Modeling, design, and analysis are the three main steps in the process. Modeling is the practise of studying a system more thoroughly via imitation. Models reflect and copy the characteristics of the system. Models outline what a system does. Design is the methodical production of objects. It describes how a system carries out its functions. Analysis is the process of dissecting a system in order to understand it better. It explains the rationale behind a system's actions or fails to do what a model says it should do. These three stages of the process overlap, and the design process repeatedly switches between them. Modeling is often the first step in the process, with the aim of comprehending the issue and creating potential solutions. In Figure 1 illustrate the embedded system.

Figure 1: Shows the embedded system.

To start solving the quad rotor issue, we may build models that convert human inputs to move laterally or vertically into instructions to the four motors to generate thrust. According to a

model, the vehicle would tilt and move laterally if the force on all four rotors is different. Then, it would construct state machines that represent the modes of operation, such as takeoff, landing, hovering, and lateral flight, using methods similar (Discrete Dynamics). The system could then combine these two kinds of models using the methods (Hybrid Systems), resulting in hybrid system models of the system that could be used to examine the changes between operating modes. Following that, mechanisms for composing models of multiple vehicles, models of interactions between a vehicle and its environment, and models of interactions among components within a vehicle would be provided by the techniques (Composition of State Machines) and 6 (Concurrent Models of Computation) systems, operating systems, wireless networks, etc.). The STARMAC architecture (reproduced with permission). When a first prototype reveals errors in the models, the models may need to be revised and taken back to the modelling stage.

A number of sensors are located at the left and bottom of the image, which the vehicle uses to locate itself and learn about its surroundings. Three boxes in the center display three different microprocessors. The low-level control algorithms necessary to keep the vehicle flying are carried out by the Robostix, an Atmel AVR 8-bit microcontroller that works without an operating system. Higher-level activities are carried out by the other two processors with the aid of an operating system. Both processors are equipped with wireless communications that ground controllers and cooperative vehicles may utilise. Analysis plays a significant role early on in a healthy design process. Models and designs will be subjected to analysis. The models may be examined for safety requirements, such as ensuring an invariant that states that a vehicle's vertical speed should not be more than 0.1 metres per second if it is within one metre of the ground. The designs may be examined for the software's timing behaviour, such as how quickly the system reacts to an emergency shutdown instruction. Details of both models and designs will be involved in certain analytical difficulties. Understanding how the system will react in the quadrotor example if network connection is lost and the vehicle cannot be reached is crucial. How does the car know when contact is lost? Accurate software and network modelling will be necessary for this.

We would next check that these safety features are met by software implementations using the methods (Equivalence and Refinement) and (Reachability Analysis and Model Checking). The methods (Quantitative Analysis) would be used to check if the programme complies with realtime restrictions approaches would be used to guarantee that the quadrotor cannot be taken over by bad parties and that whatever private information it may be acquiring is not disclosed to an enemy. The book's first section, on modelling, focuses on models of dynamic behaviour. The major topic of modelling physical dynamics is briefly covered with an emphasis on continuous dynamics in time which also emphasises how important it is for designers to understand the semantics of composition. Concurrent models of computation are covered (Concurrent Models of Computation), including many of the ones found in Simulink and LabVIEW, two popular design tools used by practitioners.

In the chapter on modelling, we describe a system as only a collection of components that are taken into account collectively. In contrast to conceptual or logical systems like software and algorithms, a physical system is one that is actualized in substance. A system's dynamics is how it changes through time, or how it evolves. A physical system model is a description of certain features of the system that aims to shed light on some of the system's characteristics. The models used in this article contain mathematical characteristics that make systematic analysis possible. Since the model replicates the system's characteristics, it provides understanding of the system.

A model is a system unto itself. It's crucial to distinguish between a model and the system it represents. There are two separate artefacts here. If a model of a system precisely captures the characteristics of the system, it is said to have high fidelity. If specifics are left out, it is called to abstract the system. Physical system models are always abstractions of the real system because they must always leave out some aspects. Developing a grasp of how to utilise models, how to take use of their strengths, and how to respect their flaws is one of this text's main objectives.

A cyber-physical system (CPS) is a system that combines computer, networking, and physical components. All three components are often included in models of cyber-physical systems. Typically, the models must capture both dynamical and static features (those that do not change during the operation of the system). It's vital to remember that a cyber-physical system model doesn't always need to incorporate both discrete and continuous components. A model that is exclusively discrete (or exclusively continuous) may have high fidelity for the desired features.

It would take more than one chapter or even one book to cover all of the modelling approaches covered in this section of the book. Such models are in fact the subject of 12 Introduction to Embedded Systems, Lee & Seshia several areas of biology, physics, chemistry, and engineering. Our strategy is geared for engineers. We begin by assuming that the reader has some familiarity with mathematical dynamics modelling (calculus courses that include physics examples are adequate), and then we concentrate on building a variety of models. The combined modelling of the cyber side, which is logical and conceptual, with the physical side, which is embodied in matter, will constitute the problem's core for the cyber-physical system. We thus avoid attempting to be exhaustive in favour of selecting a small number of well-known and often used modelling approaches, reviewing them, and then combining them to create a cyber-physical whole.

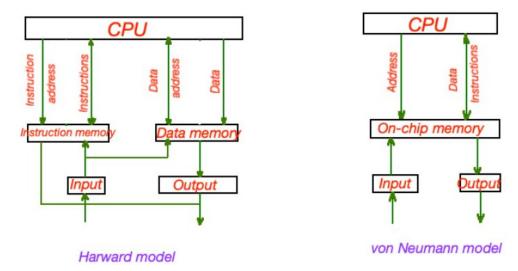

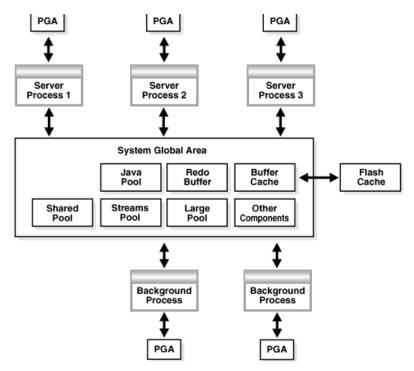

The book's second section, which reflects the subject's inherent variability, has a totally different tone. This section focuses on embedded system design with a particular emphasis on their function inside a CPS (Sensors and Actuators), with a focus on how to describe them so that their function in the dynamics of the whole system is understood. The topic of processor architectures is covered in Chapter 8 (Embedded Processors), with specific attention paid to those aspects that make embedded systems work best. Memory architectures (Memory Architectures), which also covers physical characteristics like memory technologies, architectural characteristics like memory hierarchy (caches, scratchpads, etc.), and abstractions like memory models in programming languages.

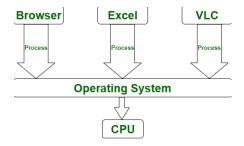

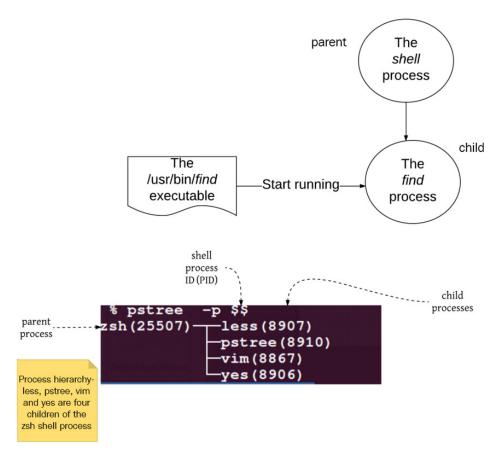

The impact of memory design on dynamics is the main focus. The digital/analog interface, including sampling, and input/output techniques in software and computer systems are covered. The concepts that underpin operating systems (Multitasking), with a focus on multitasking. The reader is intended to be persuaded that there is genuine benefit in applying the modelling approaches presented in the first part of the book by emphasising the drawbacks of using lowlevel processes like threads. These modelling methods assist designers in developing trust in system designs. Real-time scheduling is covered (Scheduling), which also introduces the topic.

Given the importance of concurrency and time control in the design of cyber-physical systems, we pay close attention to these processes in all of the design-related chapters. Embedded processors often have a specific purpose when used in a product. They can manage an automobile engine or gauge Arctic ice thickness. Increasing their specialization may have a significant positive impact. For instance, they could use a lot less power and so can be used for extended periods of time with few batteries. Or they could have specialist equipment to carry out tasks like image analysis that would be expensive to carry out on standard gear. The reader should be able to critically assess the many technological options accessible with the help of this section.

Teaching students to construct systems while thinking beyond conventional abstraction levels, such as hardware and software, computation and physical processes, is one of the objectives of this section of the book. Although this kind of cross-layer thinking is helpful when constructing systems generally, it is especially crucial in embedded systems due to their diverse nature. For instance, in order to construct a control method that is stated in terms of real-valued values, a programmer must have a firm grasp of computer arithmetic (for instance, of fixed-point numbers).

Similar to this, a developer of automotive software that must adhere to real-time limitations must be aware of processor capabilities like pipelines and caches that may influence how quickly tasks are completed and, therefore, how the system behaves in real-time. Similar to this, an implementer of interrupt-driven or multi-threaded software must be aware of the atomic operations made available by the underlying software-hardware platform and apply the proper synchronization mechanisms to guarantee accuracy. This section of the book employs homework tasks to help readers get a better knowledge of these cross-layer concepts rather than doing an extensive study of various implementation approaches and platforms.

## **CONCLUSION**

Embedded systems are a critical component of modern technology and play a vital role in a wide range of industries and applications. From consumer electronics to aerospace and defense, embedded systems are used to provide fast, reliable, and intuitive user experiences while also conserving power and extending battery life. The development of embedded systems is a complex process that requires a range of specialized skills and knowledge, from the identification of requirements to the deployment and maintenance of the final product.

## **REFERENCES:**

- [1] S. Gauhar Fatima, S. K. Fatima, S. Abdul Sattar, S. Adil, and K. F. Ahmed, "Home automation using Zigbee technology and IoT," Int. J. Adv. Res. Eng. Technol., 2019, doi: 10.34218/IJARET.10.2.2019.011.

- [2] M. N. Kapadia, P. D. Sonawane, and A. Marhatta, "Experimentation & analysis of door refrigerator," Int. J. Recent Technol. Eng., 2019, doi: 10.35940/ijrte.B3034.078219.

- M. Agrawal, J. Zhou, and D. Chang, "A survey on lightweight authenticated encryption [3] and challenges for securing industrial IoT," in Advanced Sciences and Technologies for Security Applications, 2019. doi: 10.1007/978-3-030-12330-7 4.

- T. Tumurbaatar and T. Kim, "Comparative study of relative-pose estimations from a [4]

- monocular image sequence in computer vision and photogrammetry," Sensors (Switzerland), 2019, doi: 10.3390/s19081905.

- [5] Khin Nyein Win | Lwin Lwin Htay | Nyan Phyo Aung, "Automatic Water Storage and Distribution System using Reliance SCADA," Int. J. Trend Sci. Res. Dev., 2019, doi: https://doi.org/10.31142/ijtsrd26414.

- [6] A. Ahmad, "Reliable and Fault Tolerant Systems on Chip Through Design for Testability," in Proceedings - 2019 Amity International Conference on Artificial Intelligence, AICAI 2019, 2019. doi: 10.1109/AICAI.2019.8701390.

- [7] L. A. Dobrzański and A. D. Dobrzańska-Danikiewicz, "Why are carbon-based materials important in civilization progress and especially in the industry 4.0 stage of the industrial revolution," Materials **Performance** and Characterization. 2019. doi: 10.1520/MPC20190145.

- S. Eom, R. M. Voyles, and D. Kusuma, "Embedding intelligence into smart tupperware [8] brings internet of things home," in Annual Technical Conference - ANTEC, Conference Proceedings, 2019.

- [9] A. Jain, O. Prakash, A. Talukdar, S. P. Samal, R. Nanjundappa, and N. Mahesha, "Screen intelligence engine: ML based method for predicting IoT devices using screen contents," in 2019 IEEE 16th India Council International Conference, INDICON 2019 - Symposium Proceedings, 2019. doi: 10.1109/INDICON47234.2019.9030306.

- E. Bouzekri et al., "Engineering issues related to the development of a recommender system in a critical context: Application to interactive cockpits," Int. J. Hum. Comput. Stud., 2019, doi: 10.1016/j.ijhcs.2018.05.001.

## **CHAPTER 2**

## A COMPREHENSIVE STUDY ON CONTINUOUS DYNAMICS

Ms. Natya S, Assistant Professor Department of Electronics and Communication Engineering, Presidency University, Bangalore, India Email Id- natyas@presidencyuniversity.in

## **ABSTRACT:**

Continuous dynamics is a branch of mathematics and physics that deals with the study of systems that evolve continuously over time. These systems are described by mathematical models that involve differential equations and partial differential equations, and they arise in various fields, such as mechanics, biology, economics, and engineering. The study of continuous dynamics involves the investigation of the behavior of these systems over time, including their stability, periodicity, and chaos. It also involves the analysis of their long-term behavior and the study of the effects of external perturbations on the system. Continuous dynamics has many applications in science and engineering, such as the design and control of physical systems, the analysis of ecological and economic systems, and the understanding of biological and physiological processes. It is a rich and active field of research, and it continues to provide new insights into the behavior of complex systems in the natural world.

## **KEYWORDS:**

Biology, Continuous Dynamics, Economics, Mechanics, Periodicity.

### INTRODUCTION

Continuous dynamics is a term used in physics and mathematics to describe the behavior of systems that change continuously over time. Unlike discrete dynamics, which involves systems that change in steps or jumps, continuous dynamics involves systems that change smoothly and continuously. Continuous dynamics is a fundamental concept in the study of complex systems, and it has numerous applications in fields such as physics, engineering, biology, and economics. In physics, continuous dynamics is used to describe the motion of objects and the behavior of physical systems, such as fluid flow and electromagnetic fields. In engineering, continuous dynamics is used to model and simulate the behavior of complex systems, such as control systems and manufacturing processes. In biology, continuous dynamics is used to model the behavior of biological systems, such as the growth and development of organisms. And in economics, continuous dynamics is used to model the behavior of markets and economic systems [1].

One of the key concepts in continuous dynamics is the idea of a differential equation. A differential equation is an equation that relates the rate of change of a system to its current state. In other words, it describes how the system changes over time based on its current state. Differential equations can be used to model a wide range of physical, biological, and economic systems, and they are an essential tool in the study of continuous dynamics. Another important concept in continuous dynamics is the notion of a phase space. A phase space is a mathematical representation of a system that captures all possible states of the system at a given point in time. In other words, it is a space that describes the state of the system in terms of its relevant variables. For example, in physics, the phase space of a particle might include its position and velocity. In economics, the phase space of a market might include the price and quantity of a particular commodity [2].

One of the most important ideas in continuous dynamics is the concept of attractors. An attractor is a set of states in the phase space of a system that the system tends to move towards over time. Attractors can be either stable or unstable, depending on whether small perturbations from the attractor lead the system back towards the attractor or away from it. Attractors are a key concept in the study of chaos theory, which is the study of complex, nonlinear systems that exhibit unpredictable behavior.

Another important concept in continuous dynamics is the idea of bifurcations. A bifurcation is a point in the phase space of a system where the behavior of the system changes dramatically. For example, in the case of a pendulum, a bifurcation might occur when the pendulum changes from swinging back and forth to spinning around in circles. Bifurcations are often associated with the emergence of new behavior in a system and can be used to study the stability and resilience of a system [3].

The study of continuous dynamics has led to numerous important discoveries and insights in physics, biology, economics, and many other fields. For example, in physics, the study of fluid dynamics has led to a better understanding of the behavior of fluids and the design of more efficient engines and turbines. In biology, the study of continuous dynamics has led to a better understanding of the growth and development of organisms and the spread of diseases. And in economics, the study of continuous dynamics has led to a better understanding of the behavior of markets and the factors that drive economic growth.

In conclusion, continuous dynamics is a fundamental concept in the study of complex systems that change continuously over time. It is a powerful tool that can be used to model and simulate the behavior of physical, biological, and economic systems, and it has numerous applications in a wide range of fields. By studying continuous dynamics, scientists and engineers can gain new insights into the behavior of complex systems and develop new technologies and strategies for solving some of the world's most pressing problems.

Continuous dynamics is a field of study that explores how systems change over time in a continuous and smooth manner. It is a fundamental concept in many fields of science, such as physics, engineering, biology, and economics. Continuous dynamics is based on differential equations, which relate the rate of change of a system to its current state. The study of continuous dynamics involves concepts such as phase spaces, attractors, bifurcations, and chaos theory [4].

One important application of continuous dynamics is in the field of fluid dynamics. Fluids are complex systems that change continuously over time, and the study of fluid dynamics is crucial for understanding the behavior of fluids and designing more efficient engines, turbines, and other fluid-based systems. In fluid dynamics, continuous dynamics is used to model the behavior of fluids and predict how they will behave under different conditions. For example, differential equations can be used to model the flow of water through a pipe, and phase spaces can be used to represent the different states of the water in the pipe.

Another important application of continuous dynamics is in the field of control systems. Control systems are systems that are designed to control the behavior of other systems, such as manufacturing processes, robots, and aircraft. Continuous dynamics is used to model and simulate the behavior of control systems and to design control strategies that are effective and efficient. For example, differential equations can be used to model the behavior of a robot arm, and phase spaces can be used to represent the different states of the arm.

In biology, continuous dynamics is used to model the growth and development of organisms. Biological systems are complex systems that change continuously over time, and the study of continuous dynamics is crucial for understanding how organisms grow and develop. Differential equations can be used to model the growth of a population of bacteria, and phase spaces can be used to represent the different states of the bacteria.

## LITERATURE REVIEW

Michael J. Spivey et al. The best way to characterise real-time cognition is not as a series of logical operations carried out on discrete symbols but rather as a dynamic pattern of neural activity. The consistency of these dynamics shows that mental activity does not lend itself to the language labels relied on by most of psychology when it occurs between states of consciousness that may be described. We examine eye-tracking and mouse-tracking evidence for this temporal continuity and give geometric visualisations of mental activity, portraying it as a continuous course through a state space (a multidimensional space in which locations correspond to mental states). However, the majority of the mental trajectory is in intermediate regions of that space, revealing graded mixtures of mental states. When the state of the system travels towards a frequently visited region of that space, the destination may constitute recognition of a specific word or a specific object [5].

Jan Lorenz et al. Deffuant et al. They have attracted a good deal of interest from the complexity science, sociophysics, and social simulation groups. Researchers from fields including physics, mathematics, computer science, social psychology, and philosophy are working on it. In these models, agents have ongoing views that they can progressively change if they learn what other people think. According to the theory of bounded confidence, agents can only communicate with one another if their opinions are similar. The models may also be recast based on the agent's density in the opinion space in a master equation style. Typically, the models are examined through agent-based simulations in a Monte Carlo style. The fourfold benefit of this survey. The frameworks for agent-based and density-based modelling, which include examples of multidimensional opinions and heterogeneous boundaries of confidence, will be shown first. It will also provide the cluster configuration bifurcation diagrams for the homogeneous model with evenly distributed starting beliefs [6].

Seung Yeal Ha et al. We assume that the simulation findings for the discrete dynamical systems correspond to what is occurring in the equivalent continuous dynamical systems since numerical simulations for continuous dynamical systems are based on their discretized models in time and space. This is generally true for any limited time frame given appropriate system parameter circumstances. With the help of exponential synchronisation estimates and a tight confinement of the initial phase to a small subset of the state space, we demonstrate in this paper a smooth transition from discrete dynamics to continuous dynamics for the ensemble of Kuramoto oscillators that is valid over the entire time interval. For the discrete Kuramoto model and its enhanced second-order extension, we carry out this uniform-in-time transition [7].

Yuji Yamamoto et al. From the viewpoint of a dynamical system, complex human behaviour, such as interlimb and interpersonal coordination, has been investigated. We examine how a dynamical system approach which incorporates continuous, discrete, and switching dynamics can be applied to a sports event. Using a relative phase analysis, it was discovered that during expert kendo bouts, switching between in- and anti-phase synchronisation was regulated by an interpersonal distance of 0.1 metres. Return map analysis was used on the time series of movements during kendo bouts in the discrete dynamical system. Attractors and repellers, or six coordination patterns, were used to categorise offensive and defensive actions. Furthermore, these attractors and repellers displayed two distinct states. The coordination patterns and switching behaviour were then elucidated by calculating state transition probabilities based on the two states. We proposed switching dynamics with temporal inputs to elucidate the fundamental principles underlying the complicated behaviour related to switching inputs in a striking action as a non-autonomous system [8].

Pinzeng Rao et al. The use of remote sensing data for continuous, high spatiotemporal-resolution dynamic monitoring of lake water extents is still constrained by the pervasiveness of noise, such as clouds and cloud shadows. The goal of this work is to develop a method for mapping continuously occurring time series of very precise lake water extents. Four lakes were chosen as instances from various parts of China. Two sets of MODIS products, including MOD09A1 and MOD13Q1, are utilised to extract water bodies in order to minimise the effects of noise and guarantee high spatial and temporal resolution of the final findings. This strategy primarily consists of data fusion, post processing, and preliminary categorization. The first classification results were effectively and automatically obtained using the Random Forest (RF) classifier. Post-processing is used to fix the noise-affected classification findings as much as feasible. [9].

Glenn J. Martyna et al. Unfortunately, for tiny or rigid systems, the Nosé-Hoover dynamics is not ergodic. Here, a change to the dynamics is suggested that uses a Nosé-Hoover chain instead of a single thermostat variable. The canonical distribution is provided by the "new" dynamics, when the basic formalism fails. In addition, the new technique is simpler to use than an extension which likewise produces the canonical distribution for stiff instances. The Homologous Data-Based Spatial and Temporal Adaptive Fusion Method (HDSTAFM), which lessens the impact of noise and also improves the temporal and spatial resolution for the final water results, is used to fuse the processed results of the two sets of products. Landsat-based water data were used to measure accuracy, and the values for overall accuracy (OA), user's accuracy (UA), producer's accuracy (PA), and kappa coefficients (KC) are often more than 0.9. A time series of water area and altimetry data collected by several satellites, as well as water-level data chosen from hydrological stations, both showed good agreement [10].

Denis Stijepic et al. We go through the continuous dynamics models on the 2-simplex that result from applying various qualitative constraints on the (continuous) functions that produce the dynamics on the 2-simplex. We take into account three different categories of qualitative constraints: inequality conditions (or set-theoretical conditions), monotonicity/curvature conditions (or differential-geometrical conditions), and topological conditions (which refer to (transversal) non-(self-) intersection of trajectories). We go through the effects of these limitations on transitional and limit dynamics on the 2-simplex as well as the many prospective and actual uses of the resultant system-theoretical models in economics, and in particular in economic growth and development theory [11].

#### DISCUSSION

Chaos theory is another important aspect of continuous dynamics. Chaos theory is the study of complex, nonlinear systems that exhibit unpredictable behavior. Chaotic systems are characterized by their sensitivity to initial conditions, which means that small changes in the initial conditions can lead to large differences in the behavior of the system over time. Chaos theory has applications in many fields, such as meteorology, economics, and biology. For example, chaotic behavior can be observed in the weather, the stock market, and the behavior of the heart.

Attractors are another important concept in continuous dynamics. An attractor is a set of states in the phase space of a system that the system tends to move towards over time. Attractors can be either stable or unstable, depending on whether small perturbations from the attractor lead the system back towards the attractor or away from it. Attractors are a key concept in the study of chaos theory, as they can help to explain the behavior of chaotic systems. Attractors also have applications in many fields, such as in the design of control systems, where they can be used to stabilize the behavior of a system.

Bifurcations are another important concept in continuous dynamics. A bifurcation is a point in the phase space of a system where the behavior of the system changes dramatically. For example, in the case of a pendulum, a bifurcation might occur when the pendulum changes from swinging back and forth to spinning around in circles. Bifurcations are often associated with the emergence of new behavior in a system and can be used to study the stability and resilience of a system.

Continuous dynamics is a powerful tool for understanding the behavior of complex systems. By studying continuous dynamics, scientists and engineers can gain new insights into the behavior of physical, biological, and economic systems and develop new technologies and strategies for solving some of the world's most pressing problems. For example, the study of continuous dynamics has led to the development

A few of the several modelling approaches for examining the dynamics of a physical system are reviewed in this chapter. We start by investigating moving mechanical components (classical mechanics). The methods utilised to research these components' dynamics generally to a wide range of different physical systems, including as circuits, chemical processes, and biological processes. However, as mechanical components are the most easily seen by most people, they provide our example concreteness. Differential equations, or their counterpart, integral equations, are often used to simulate the motion of mechanical components. These models are only truly effective for "smooth" motion, which may be defined more precisely using the concepts of linearity, temporal invariance, and continuity.

For movements that are not smooth, such as those depicting collisions of mechanical components, we may utilise modal models that represent. Mechanical item collisions may be effectively described as discrete, instantaneous occurrences. Hybrid systems modelling, which entails simultaneously simulating smooth motion and such discrete occurrences, is covered in Chapter 4. We are one step closer to combined modelling of cyber and physical processes thanks to such mixtures of discrete and continuous behaviours.

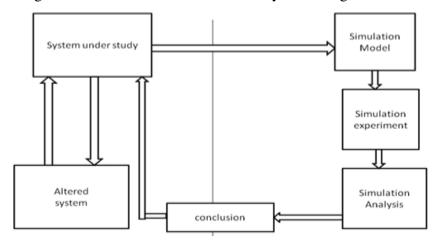

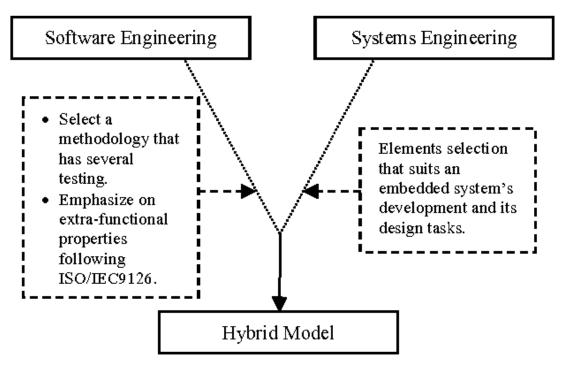

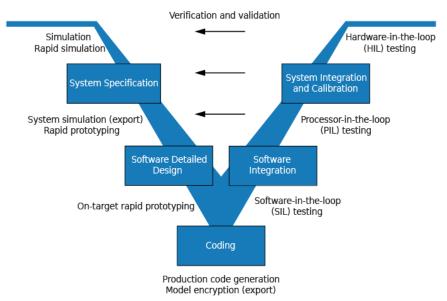

We start with basic equations of motion that provide the form of ordinary differential equations, modelling the system (ODEs). Then, we demonstrate how these ODEs may be represented in actor models, a class of models found in well-known modelling languages like Simulink (from The MathWorks, Inc.) and LabVIEW (from National Instruments). Then, we analyse the characteristics of these models, such as linearity, temporal invariance, and stability, and we consider how these characteristics affect model manipulation. We provide a straightforward illustration of a feedback control system that grounds an unsteady system. Such systems are a prime example of a cyber-physical system since software is often used to implement their controllers. The characteristics of the cyber and physical components influence those of the entire system. In Figure 1 shows the embedded control system design and simulation.

Figure 1: This shows the Embedded Control System Design.

This is not meant to be exhaustive; rather, it is meant to be just enough to allow you to build fascinating models. Many outstanding books on classical mechanics are recommended to the interested reader, including Goldstein (1980), Landau and Lifshitz (1976), Marion and Thornton, and others (1995). Physical objects' motion in space may be described using six degrees of freedom. Three of them indicate three-dimensional position, and three of them represent spatial orientation. By convention, x is drawn increasing to the right, y is drawn rising up, and z is drawn increasing out of the page.

Three axes, x, y, and z, are assumed. Roll  $\theta x$  is an angle of rotation about the x axis, where by convention an angle of 0 radians denotes horizontally flat along the z axis (i.e., the angle is provided relative to the z axis). The rotation around the y-axis is known as yaw, and according to convention, an angle of 0 radians is equivalent to pointing straight to the right (i.e., the angle is provided relative to the x-axis). Rotation around the z axis is referred to as pitch, and 0 radians is used to denote horizontal pointing in this context (i.e., the angle is given relative to the x axis).

Therefore, six functions of the type f: R, where the domain is time and the codomain is either distance along an axis or angle with respect to an axis, may be used to describe the location of an object in space. Newton's second law, which links force with acceleration, governs changes in position or orientation. The second derivative of position is acceleration. The position information is handled by our first equation, F(t) = Mx (t), in which F is the force vector in three directions, M is the object's mass, and x is x's second derivative with respect to time (i.e., the acceleration). Velocity is essential.

2A continuous-time signal may only have a linked subset of R as its domain, such as R+, the non-negative reals, or the range from 0 to 1 inclusive. Although the codomain may be any set, real numbers are the most effective for describing physical quantities x(t) = x(0) + Z t 0 x ()d = x(0) + tx(0) + 1 M Z t 0 Z 0 F()dd, where x(0) is the starting position. Position is the integral of velocity. You may calculate an object's acceleration, velocity, and position at any time using these equations if you know its beginning location, initial velocity, and the forces acting on it in all three directions as a function of time.

Torque, the rotating equivalent of force, is used in the versions of these equations of motion that alter orientation. The net rotational force acting on an item is represented as a three-element vector as a function of time. Similar to equation (2.1), T(t) = d dt I(t) (t), (2.2), where T is the torque vector in three directions and I(t) is the object's moment of inertia tensor, it may be connected to angular velocity. The object's shape and orientation determine the 3 3 matrix that represents the moment of inertia. Intuitively, it describes the reluctance that an item has to spin about any axis as a function of its orientation along the three axes. If the object is spherical, for example, this reluctance is the same along all axes, hence it simplifies to a \sconstant scalar I (or equivalently, to a diagonal matrix I with equal diagonal elements I).

For instance, in this case, Iyx(t) is the inertia that governs how acceleration around the x axis is connected to torque around the y axis and Ty(t) is the net torque around the y axis (which would induce changes in yaw). Rotational velocity is the integral of acceleration, where (0) is the starting rotational velocity in three axes. Rotational velocity is expressed as (t) = (0) + Z t 0 () d. Using (2.3), this becomes (t) = ((0) + 1 I Z t 0 T(d)) for a spherical object.

The rotational velocity's integral formula for orientation is (t) = (0) + Z t 0 (d) = (0) + t (0) + 1 IZ t 0 Z 0 T()dd, where (0) is the starting orientation. These equations allow you to calculate the rotational acceleration, velocity, and orientation of an item at any moment provided you know it beginning orientation, initial rotational velocity, and the torques acting on it in all three axes as a function of time.

Sometimes we may simplify by lowering the number of dimensions that are taken into account, as we have done with a spherical object. Such a simplification is often referred to as a modelorder reduction. For instance, there may not be much need to take into account the object's pitch or roll if it is a moving vehicle on a level surface. Consider a simple control issue that allows for such dimensionality reduction. A helicopter has two rotors: one up top that gives it lift, and one on the tail that gives it motion. The helicopter's body would spin if the tail rotor weren't there.

That spin is countered by the rotor on the tail. In particular, the main rotor's torque must be balanced by the force generated by the tail rotor. Here, we examine the tail rotor's function apart from the helicopter's other motions. There is no need to take equations defining position into consideration since we are assuming that the helicopter's location is fixed at the origin. Additionally, because we believe the helicopter would stay vertical, pitch and roll are set at zero. Since we can specify the coordinate system to be fixed to the helicopter, these assumptions are not as implausible as they may seem.

According to these presumptions, the moment of inertia transforms into a scalar that symbolises a torque that prevents yaw variations. The variations in yaw will be due to Newton's third law, the action-reaction law, which asserts that every action has an equal \sand opposite response. As a result, the helicopter will probably start to spin anticlockwise to the direction of the rotor. In order to prevent the body of the helicopter from spinning, the tail rotor's role is to counteract that torque.

A system that receives as input a continuous-time signal Ty, the torque around the y axis, is used to represent the simplified helicopter (which causes changes in yaw). This Torque is the result of adding the forces produced by the main and tail rotors. That total equals 0 when things are fully balanced. Our system will produce the angular velocity y around the y axis as its output. It is possible to write (2.2) in dimensionally reduced form as y(t) = Ty(t)/Iyy. The crucial note about this example is that if we were to choose to describe the helicopter by, say, having x:  $R \rightarrow R \s3$ \srepresent the absolute location in space of the tail \sof the helicopter, we would end up with a significantly more sophisticated model. The control system's design would likewise be significantly more challenging.

A differential or integral equation that connects input signals (force or torque) to output signals (position, orientation, velocity, or rotational velocity) provides a model of a physical system in the preceding section. Such a physical system may be considered as a component in a bigger system. In specifically, a box having an input port and an output port may be used to mimic a continuous-time system, which uses continuous-time signals:

Here, the codomain denotes the signal's value at a certain moment, while the domain denotes time. If we want to explicitly represent a system that exists and begins to function at a certain moment in time, we may swap out the domain R with R+, the non-negative reals. The collection of functions that translate the reals into the reals, such as x and y above, is what makes up the system's model, and it has the form S: X Y, (2.5), where X = Y = R R.

The parameters of the system may affect how the function S behaves, in which case they may be optionally indicated in the box and optionally written in the function notation. If there are parameters p and q in the aforementioned figure, for instance, the system function may be written as Sp,q or even S(p,q), bearing in mind that both notations reflect functions of the type in 2.5. An actor is a box like the one in the example above, where the inputs are functions and the outputs are functions.

Both the input and the output are functions with continuous time. The actor's starting angular velocity (y(0)) and moment of inertia (Iyy) are its parameters. The following criteria characterise the actor's role. Models of actors may be constructed. Particularly, given two actors S1 and S2, we may create the following cascade composition: The set of all functions with domain R and codomain R is denoted by the notation R R, which may alternatively be written (R R). The "wire" connecting the output of S1 and the input of S2 signifies exactly that y1 = x2, or more pedantically,  $\$   $t \in R$ , y1(t) = x2(t).

We may express this equation more succinctly by writing y1 = ax1, where it is clear that the result of a scalar and a function x1 is equivalent. The right actor is a representation of an integrator parameterized by starting value I as described by t R, y2(t) = I + Z t 0 x2(d)d.

We can see that this system reflects, where the input x1 = Ty is torque and the output y2 = y is angular velocity, if we set the parameter values to a = 1/Iyy and I = y(0). The boxes that depict the actors in the above illustration are our own iconography. Assigning those recognized visual notations is helpful since these specific actors (scaler and integrator) are especially effective building blocks for constructing models of physical dynamics.

Actors with multiple input signals and/or multiple output signals are a possibility. Similar representations of these may be seen in the example below, which includes two input signals and one output signal: A signal adder is a very helpful construction piece with this shape, defined by t R, y(t) = x1(t) + x2(t). When one of the inputs is sometimes subtracted rather than added, the icon is further modified to include a negative sign next to that input, as seen below: A function S is represented by this actor: Given by (R R), (S(x1, x2))(t) = y(t) = x1(t) x2 and (t R), (R R) 2 (R)R) (t).

Unless the difference is crucial to the argument, we won't distinguish between a system and its actor model in the remaining sections of this chapter. We'll assume that the actor model adequately represents all of the system's interesting aspects. This is a big assertion, to be sure. The actor model's attributes often only provide rough descriptions of the real system. In this part, we examine some possible characteristics of actors and the systems they comprise, such as causality, memorylessness, linearity, temporal invariance, and stability. A system is logically considered causal if its output is solely dependent on its recent and previous inputs. It is a little difficult to make this idea exact, however. We do this by first noting "present and prior inputs." Take into account the continuous-time signal x: R A for some set A.