# ARCHIVES OF VLSI TECHNOLOGY

Dr. Ashutosh Anand Dr. Sachin Gupta

**ARCHIVES OF VLSI TECHNOLOGY**

# **ARCHIVES OF VLSI TECHNOLOGY**

Dr. Ashutosh Anand Dr. Sachin Gupta

Published by: Alexis Press, LLC, Jersey City, USA www.alexispress.us © RESERVED

This book contains information obtained from highly regarded resources. Copyright for individual contents remains with the authors. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereinafter invented, including photocopying, microfilming and recording, or any information storage or retrieval system, without permission from the publishers.

> For permission to photocopy or use material electronically from this work please access alexispress.us

#### First Published 2022

A catalogue record for this publication is available from the British Library

Library of Congress Cataloguing in Publication Data

Includes bibliographical references and index.

Archives of VLSI Technology by Dr. Ashutosh Anand, Dr. Sachin Gupta

ISBN 978-1-64532-877-3

# **CONTENTS**

| Chapter 1. Introduction to VLSI Technology                                                                                     | 1       |

|--------------------------------------------------------------------------------------------------------------------------------|---------|

| — Dr. Ashutosh Anand                                                                                                           |         |

| Chapter 2. Hardware Development of VLSI                                                                                        |         |

| — Dr. K Bhanu Rekha                                                                                                            |         |

| Chapter 3. Advancements in Physics-Based EM Modeling: Techniques and Applications for Characterizing Electromagnetic Phenomena |         |

| — Dr. Manikandan M                                                                                                             |         |

| Chapter 4. MEMS-Based IMU for Pose Estimation                                                                                  |         |

| — Dr. Ashutosh Anand                                                                                                           |         |

| Chapter 5. Data Flow Verification in SOC Using Formal Techniques                                                               |         |

| — Dr. Joseph Anthony Prathap                                                                                                   |         |

| Chapter 6. Mitigating Cyber security Risks with Intrusion Prevention Systems and<br>Intellectual Property Protection           |         |

| — Ms. Akshaya M Ganorkar                                                                                                       |         |

| Chapter 7. Very Large-Scale Integration VLSI System                                                                            |         |

| — Dr. Sivaperumal S                                                                                                            |         |

| Chapter 8. Metal–Oxide–Semiconductor Field-Effect Transistor with a Vacuum Chan<br>— Dr. S Riyaz Ahammed                       | nnel 59 |

| Chapter 9. Importance of VLSI in modern days and Uses of VLSI                                                                  |         |

| — Dr. Sachin Gupta                                                                                                             |         |

| Chapter 10. Recent Trends in Medical Imaging by using VLSI                                                                     | 76      |

| — Dr. Rahul Kumar                                                                                                              |         |

| Chapter 11. VLSI: Development and Basic Principles of IC Fabrication                                                           | 84      |

| Chapter 12. The Future of Very Large-Scale Integration (VLSI) Technology                                                       | 91      |

| Chapter 13. Equivalence Transforms for Recursive Computations<br>— Dr. Vikas Sharma                                            |         |

| Chapter 14. Developing an Adequate Simulation Strategy<br>— Dr. Rajbhadur Singh                                                | 106     |

| Chapter 15. Clocking of Synchronous Circuits                                                                                   | 113     |

| Chapter 16. The Data Consistency Problem of Scalar Acquisition                                                                 | 121     |

| Chapter 17. The Metastable Synchronizer Behavior                                                                                                                 |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| — Mr. Lokesh Lodha                                                                                                                                               |    |

| Chapter 18. A Conceptual Study on Electrical CMOS Contraptions                                                                                                   | 38 |

| Chapter 19. Understanding and Mitigating the Effects of Ground Bounce and<br>Supply Droop in Digital Circuits                                                    | 47 |

| Chapter 20. Exploring the Characteristics and Applications of Conducting Layers in<br>Electronics and Optoelectronics                                            | 53 |

| — Mr. Lokesn Loana<br><b>Chapter 21.</b> The Cell-Based Back-End Design                                                                                          | 60 |

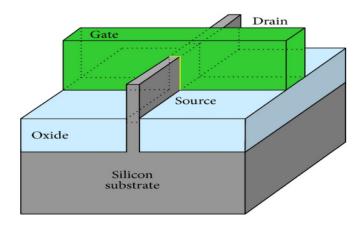

| Chapter 22. The Method of Post-layout Design Verification                                                                                                        | 68 |

| Chapter 23. Programmable Logic Arrays: A Comprehensive Review of Architecture,<br>Design, and Applications                                                       | 76 |

| — Prof. Sudhir Kumar Sharma                                                                                                                                      |    |

| <ul> <li>Chapter 24. Globally Asynchronous Locally Synchronous (GALS) Systems:</li> <li>A Review of Design Methodologies, Applications, and Challenges</li></ul> | 84 |

## **CHAPTER 1**

#### INTRODUCTION TO VLSI TECHNOLOGY

Dr. Ashutosh Anand, Assistant Professor Department of Electronics and Communication Engineering, Presidency University, Bangalore, India Email Id- <u>ashutoshanand@presidencyuniversity.in</u>

#### **ABSTRACT:**

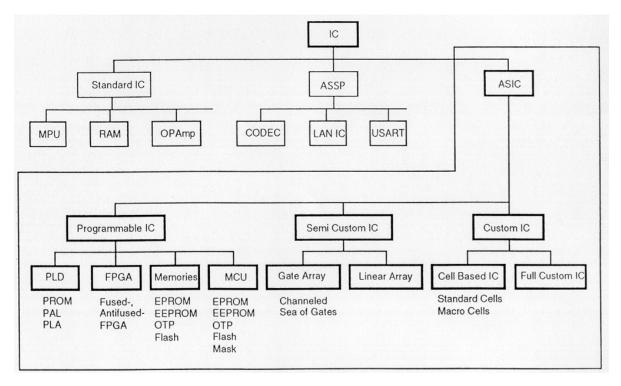

Very Large Scale Integration (VLSI) technology is a field of microelectronics that deals with the fabrication of integrated circuits (ICs) by combining thousands or even millions of transistors and other components on a single chip. The miniaturization of electronic devices has led to the development of VLSI technology, which allows for the creation of complex and powerful ICs. VLSI technology has revolutionized the electronics industry by enabling the production of smaller, faster, and more powerful devices. The development of VLSI technology has made it possible to integrate more functionality into a single chip, leading to a wide range of applications such as microprocessors, memory chips, digital signal processors, and application-specific integrated circuits (ASICs).

#### **KEYWORDS:**

ASIC, Integrated Circuit, Electronic Circuit, memory chips, VLSI.

#### **INTRODUCTION**

A CPU, RAM, ROM, and other components are often included in electrical circuits on a single PCBA. However, an IC designer has the option to combine all of these onto a single chip thanks to very large-scale integration (VLSI) technology. We can find evidence of the electronics industry's explosive expansion if we look over the previous several decades. Enhanced functionality, enhanced miniaturisation, and higher performance are all advantages. There is less room for mistake as a result of the need to insert more components while using less space. With that in mind, it makes sense why silicon (CMOS) technology has emerged as the preferred method of manufacture for VLSI circuits that are reasonably priced and of great performance during the last several years.

The technique of embedding or integrating tens of millions of semiconductors onto a single silicon semiconductor microchip is known as very large-scale integration. VLSI technology was first developed in the late 1970s, at the same time when high level processor (computer) microchips have been beginning to take shape. The microcontroller and the microprocessor are two of the most popular VLSI components.VLSI is an acronym for a kind of integrated circuit that has several devices on a computer device [1]. Naturally, the phrase dates back to the 1970s, along with a variety of other grade assimilation categorization depending on the quantity of gated or semiconductors in an integrated circuit (IC)

The development of large-scale integration technologies is principally responsible for the electronics industry's impressive expansion. The capabilities for ICs in controller, communication, slightly elevated computing, and electrical goods however are expanding thanks to the introduction of VLSI designs. Due to VLSI technology, technological advances like telephones and cellphone telecommunications provide never-before-seen levels of mobility, processing power, and application access. Forecasts for this trend point to a fast rise

as demand keeps rising. The main benefits of VLSI technology are as follows circuit size reduction increased device cost-effectiveness an increase in the engine speed of circuits and better performance less power is used than separate components increased device dependability less room is needed, and downsizing is encouraged.

#### The VLSI IC Design Process

#### VLSI IC design generally consists of two main stages or components:

- a) Digital design utilising an arduino ide software, such as Verilog, System Computer architecture, and VHDL, is referred to as front-end design. Additionally, this step includes design assurance via emulation and other types of verification. Designing, which begins with the valves and continuing thorough design with testing process, is also a part of the complete process[2], [3].

- b) Qualification and CMOS database design allows up the back-end design. Formal definition plus failure simulation are also included.

- c) The whole front architecture steps are as follows, and the complete design process is step-by-step:

- d) Problem Description: This is a system's high-level interpretation. We discuss the important factors, including design methods, usability, performance, production methods, and physical dimensions. The horsepower, versatility, performance, and volume of the VLSI technology are all included in the final specs.

- e) Architecture Definition: This covers basic requirements like floating-point units, the choice of system to employ, such as RISC or CISC, and the size of the ALU cache.

- f) Functional Design: This identifies the key functional components of a system, allowing for the determination of each component's physical and electrical requirements as well as connectivity needs.

- g) Control flow, Boolean operations, word format, and bank allocation are all part of the logic design process.

Circuit Design: In this phase, the realization of the circuit as a netlist is carried out. Even though this is a programming process, the output is checked using simulation. Tangible Model: In this phase, the layout is created by transforming the circuit into a geometry representation. Additionally, this stage adheres to certain predetermined static criteria, such as the omega rules, which provide accurate information on the ratio, component spacing, and size.

VLSI architecture design is concerned with deciding on the necessary hardware resources for solving problems from data and/or signal processing and with organizing their interplay in such a way as to meet target specifications defined by marketing. The foremost concern is to get the desired functionality right. The second priority is to meet some given performance target, often expressed in terms of data throughput or operation rate [4].

A third objective, of economic nature this time, is to minimize production costs. Assuming a given fabrication process, this implies minimizing circuit size and maximizing fabrication yield so as to obtain as many functioning parts per processed wafer as possible. Another general concern in VLSI design is energy efficiency. Battery-operated equipment, such as hand-held cellular phones, laptop computers, digital hearing aids, etc.

#### DISCUSSION

Obviously imposes stringent limits on the acceptable power consumption. It is perhaps less evident that energy efficiency is also of interest when power gets supplied from the mains. The reason for this is the cost of removing the heat generated by high-performance high-density ICs. While the VLSI designer is challenged to meet a given performance figure at minimum power in the former case, maximizing performance within a limited power budget is what is sought in the latter.

The ability to change from one mode of operation to another in very little time, and the flexibility to accommodate evolving needs and/or to upgrade to future standards are other highly desirable qualities and subsumed here under the term agility [5]. Last but not least, two distinct architectures are likely to differ in terms of the overall engineering effort required to work them out in full detail

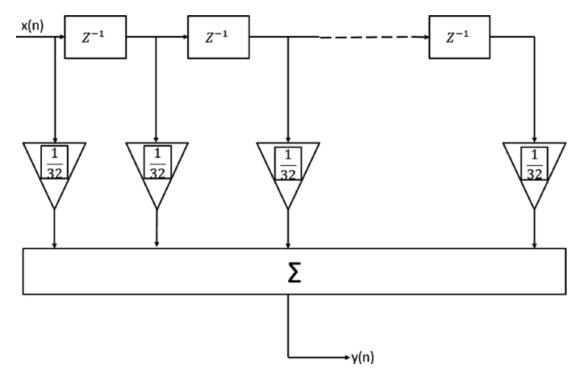

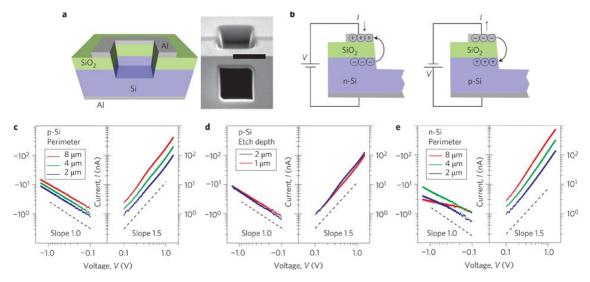

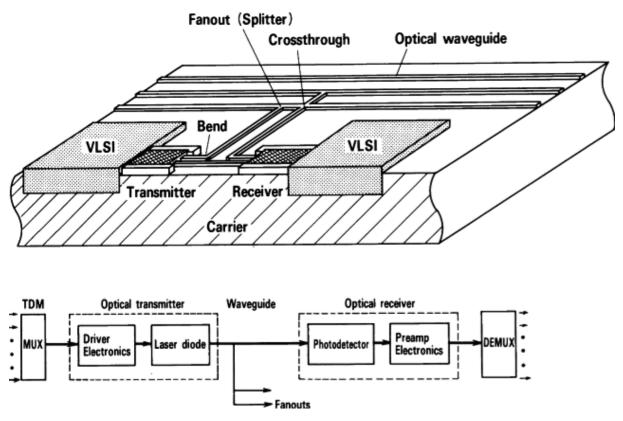

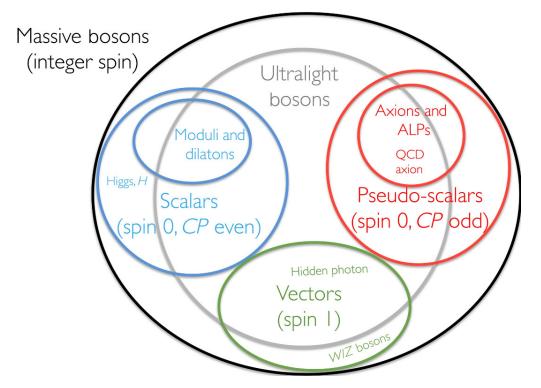

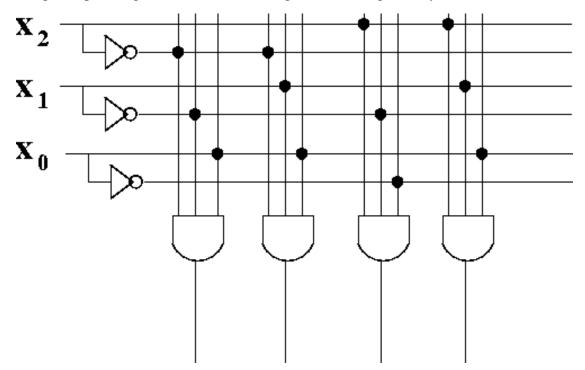

Driven by dissimilar applications and priorities, hardware engineers have, over the years, devised a multitude of very diverse architectural concepts which we will try to put into perspective how their respective strengths can be combined into one architecture. After the necessary groundwork for architectural analysis has been laid in subsequent sections will then discuss. In Figure 1 illustrate the VLC design principles.

Figure 1: Illustrate the principle of VLC design.

To select, arrange, and improve the necessary hardware resources in an efficient way with a focus on dedicated architectures is concerned with organizing computations of combinational nature. Extends our analysis to no recursive sequential computations before time wise recursive computations are addressed other than word-level computations on real numbers. Inserted in between is section 2.5 that discusses the options available for temporarily storing data and their implications for architectural decisions. Given some computational task, one basically has the choice of writing program code and running it on a program-controlled machine, such as a microprocessor or a digital signal processor (DSP), or of coming up with a hardwired electronic circuit that carries out the necessary computation steps. This fundamental dichotomy, which is described implies that a systems engineer has to make a choice:

- a) Select a processor-type general-purpose architecture and write program code for it, or

- b) Tailor a dedicated hardware architecture for the specific computational needs.

Deciding between a general-purpose processor and an architecture dedicated to the application at hand is a major decision that has to be made before embarking on the design of a complex circuit. A great advantage of commercial microprocessors is that developers can focus on higher-level issues such as functionality and system-level architecture right away. There is no need for them to address all those exacting chores that burden semi- and even more so full-custom design.

There is no need for custom fabrication masks opting for commercial instruction-set processors and/or FPL sidesteps many technical issues that absorb much attention when a custom IC is to be designed instead. Conversely, it is precisely the focus on the payload computations, and the absence of programming and configuration overhead together with the full control over every aspect of architecture, circuit, and layout design that make it possible to optimize performance and energy efficiency.

Such as power distribution, clock preparation and distribution, input/output design, physical design and verification, signal integrity, electrical overstress protection, wafer testing, and package selection, all to be discussed in forthcoming chapters. Setting up a working CAE/CAD design flow typically also is a major stumbling block, to say nothing of estimating sales volume, hitting a narrow window of opportunity, finding the right partners, and providing the necessary resources, in-house expertise, and investments.

Also note that field-programmable logic (FPL) frees developers from dealing with many of these issues too. General purpose Special purpose Algorithm any, not known a priori fixed, must be known Architecture instruction set processor, dedicated design, Harvard style no single established pattern Execution model fetch–load–execute–store cycle process data item and pass on. Datapath universal operations, specific operations only, ALU(s) plus memory customized design Controller with program microcode typically hardwired Performance instructions per second, data throughput, indicator run time of various can be anticipated benchmark programs analytically Paradigm from craftsman in his machine shop division of labor in a factory manufacturing working according to set up for smooth production different plans every day of a few closely related goods

Possible hardware standard  $\mu$ ClDSP components ASIC of dedicated architecture implementations or ASIC with on-chip  $\mu$ ClDSP or FPL (FPGAlCPLD) Engineering effort mostly software design mostly hardware design Strengths highly flexible, room for max performance, immediately available, highly energy-efficient, routine design flow, lean circuitry. Upon closer inspection, one finds that dedicated architectures fare much better in terms of performance and/or dissipated energy than even the best commercially available general-purpose processors in some situations, whereas they prove a dreadful waste of both hardware and engineering resources in others.

Algorithms that are very irregular, highly data-dependent, and memory-hungry are unsuitable for dedicated architectures. Situations of this kind are found in electronic data processing such as databank applications, accounting, and reactive systems like industrial control, user interfaces. A system is said to be reactive if it interacts continuously with an environment, at a speed imposed by that environment. The system deals with events and the mathematical formalisms for describing them aim at capturing the complex ordering and causality relations between events that may occur at the inputs and the corresponding reactions events themselves at the outputs. Examples: elevators, protocol handlers, anti-lock brakes, process controllers, graphical user interfaces, operating systems.

As opposed to this, a transformation system accepts new input values often at regular intervals uses them to compute output values, and then rests until the subsequent data items

arrive. The system is essentially concerned with arithmetic/logic processing of data values. Form alism s for describing transform systems capture the numerical dependencies between the various data items involved. Examples: filtering, data compression, ciphering, pattern recognition, and other applications colloquially referred to as number crunching but also compilers and payroll programs.

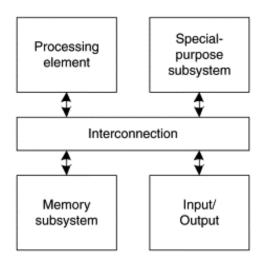

Program-controlled general-purpose processor (a) and dedicated (special-purpose) hardware structure as architectural antipodes and others. In search of optimal architectures for such applications, one will invariably arrive at hardware structures patterned after instruction set processors. Writing code for a standard microcomputer either bought as a physical part or incorporated into an ASIC as a megacell or as a virtual component is more efficient and more economic in this case.

Situations where data streams are to be processed in fairly regular ways offer far more room for coming up with dedicated architectures. Impressive gains in performance and energy efficiency over solutions based on general-purpose parts can then be obtained. Generally speaking, situations that favor dedicated architectures are often found in real-time applications from digital signal processing and telecommunications such as

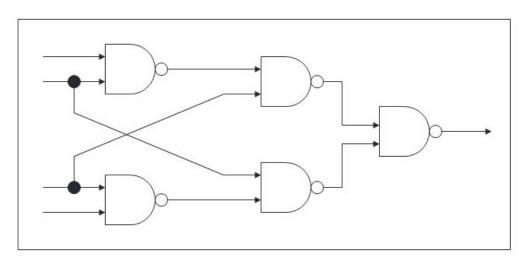

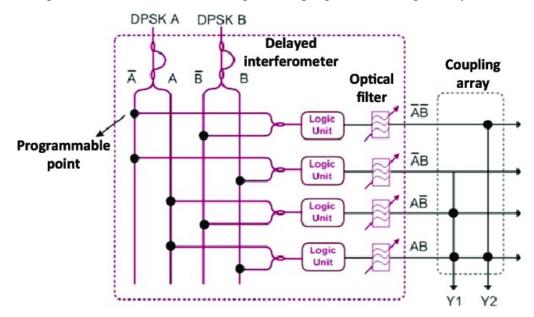

DSPs are at their best for sustained multiply–accumulate operations and offer word widths of 32 bit or so. However, as the Viterbi algorithm can be arranged to make no use of multiplication and to make do with word widths of 6 bit or less, DSPs cannot take advantage of these resources. A pipeline of tailor-made stages optimized for branch metric computation, path metric update, and survivor path trace back operations, in contrast, makes it possible to exploit the parallelism inherent in the Viterbi algorithm. In Figure 2 illustrate the design of VLCC.

#### Figure 2: Illustratethe VLCC design Flow.

Diverse throughput requirements can be accommodated by trading the number of computational units in each stage for throughput. Sophisticated DSPs, such as the C6455, include an extra coprocessor to accelerate path metric update and survivor trace back. The

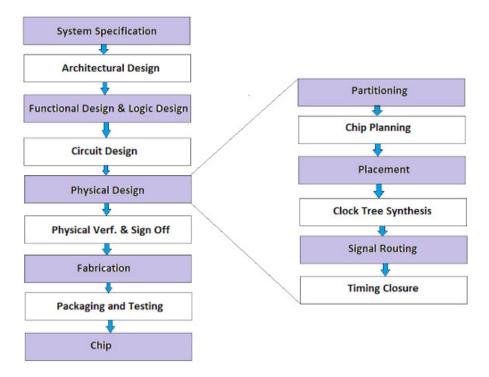

process of creating a VLSI chip involves several steps, including design, fabrication, testing, and packaging. The design phase involves creating a circuit layout using computer-aided design (CAD) software, which is then used to manufacture the chip using photolithography and other fabrication techniques. The fabricated chip is then tested to ensure its functionality and performance, and finally packaged for use in electronic devices.

The development of VLSI technology has driven the growth of the electronics industry and has had a significant impact on many aspects of modern life. The ongoing advancement of VLSI technology continues to bring new and exciting innovations to the field of electronics, including the development of faster and more powerful computers, the Internet of Things, and smart devices. There are many different duties that electronic devices today carry out in everyday life.

Certain mechanical, hydraulic, or other mechanisms have been replaced by electronic systems because they are often smaller, more adaptable, and simpler to maintain. In certain instances new uses have been made possible by electronic systems. Electronic systems carry out a range of activities, some of which are more obvious than others.

- a) Portable MP3 players and DVD players are examples of personal entertainment devices that use very little energy to execute complex algorithms.

- b) Electronic systems in automobiles regulate fuel injection systems, adjust suspensions for uneven terrain, and carry out the control tasks necessary for anti-lock braking (ABS) systems. They also run sound systems and displays.

- c) Digital electronics compress and decompress video, even at highdefinition data rates, onthe-fly in consumer gadgets.

- d) Despite their specific purpose, low-cost terminals for Web surfing nonetheless need complex circuitry.

- e) Workstations and personal computers provide text processing, financial analysis, and gaming. Central processing units (CPUs) and specialised hardware for speedier screen display, disc access, etc. are both found in computers. IP-Based Design.

- f) Medical electronic devices assess body activities and perform complex processing algorithms to alert about unexpected circumstances.

Far from overwhelming customers, the availability of these sophisticated systems merely increases demand for more complex systems. The difficulty of designing and producing integrated circuits and electronic systems is continuously rising as a result of the increasing sophistication of applications. The diversity of this group of systems is arguably its most astounding feature; as systems become more complicated, we develop fewer general-purpose computers and an increasing number of systems with specialised functions. While the increased needs of customers continue to push the boundaries of design and manufacturing, our capacity to do so is a credit to our developing mastery of both integrated circuit production and design. The qualities of integrated circuits what we can and cannot put in an integrated circuit efficiently largely dictate the design of the overall system, even though we shall focus on integrated circuits in this book. Integrated circuits significantly enhance several key system properties. Compared to digital circuits made from discrete components, ICs offer three major advantages:

In contrast to the millimetre or centimetre scales of discrete components, transistors and wires in integrated circuits are substantially smaller. As smaller components have less parasitic resistances, capacitances, and inductances, they are faster and use less power. Compared to switching between chips, switching signals between logic 0 and logic 1 inside a semiconductor can be done far more quickly. As compared to communication between chips on a printed circuit board, chip-to-chip communication may happen hundreds of times quicker. Due to fewer components and connections having lower parasitic capacitances to slow down the signal, on-chip circuits operate at fast speeds.

Moreover, a chip uses substantially less power during logic processes. Again, smaller circuits on the chip result in reduced power consumption because parasitic capacitances and resistances are driven by less power owing to their smaller size.

System and VLSI At the system level, these advantages of integrated circuits translate into benefits: Physically smaller. Consider handheld mobile phones or portable TVs, where size is often a benefit. A single chip may minimise overall power usage by taking the place of many common components. A smaller, less expensive power supply may be utilised; as less heat is generated, a fan may no longer be required; and a simpler cabinet with less electromagnetic shielding may also be conceivable. Lowering power usage has a knock-on impact on the remainder of the system. A lower price. Reduced component counts, power supply needs, cabinet prices, and other factors all result in lower system costs. Although while bespoke ICs individually cost more than the conventional components they replace, the cost of a system made of them might be lower due to the cascading effects of integration.

Understanding IC manufacturing technology as well as the economics of ICs and digital systems is necessary to comprehend why integrated circuit technology has such a significant impact on the design of digital systems. The foundation of integrated circuit technology is in our capacity to produce enormous quantities of very tiny components; now, California produces more transistors annually than the state receives in precipitation. This section provides a quick overview of VLSI production. Technology the majority of industrial processes have a close relationship with the product they are producing. For instance, a Buick assembly line would need a modest rearrangement to establish a Chevrolet assembly line; equipment like sheet metal molds would need to be changed, and certain machines could even require modification. Moreover, neither assembly line would come close to being able to create electric drills[6], [7].

On the other side, integrated circuit fabrication technology is incredibly adaptable. CMOS, bipolar, and other circuit types have various manufacturing procedures, yet any of those circuit types may be produced on a production line by just switching out a few common tools called masks. One CMOS manufacturing facility, for instance. By altering the masks that create the patterns of wires and transistors on the chips, Digital Systems and VLSI are able to produce both microprocessors and microwave oven controllers. The base material for making integrated circuits is silicon wafers. Wires and transistors are created on the wafer using patterns created during the manufacturing process. A wafer is patterned with a succession of identical chips, with some room left over for test circuit designs that enable manufacturers to gauge the effectiveness of the manufacturing process. Since we can process a single wafer to create several identical chips, the IC manufacturing method is effective. We control the digital circuit that will be produced by altering the masks that dictate what patterns are imprinted on the chip. The IC fabrication line is a versatile manufacturing platform that can be swiftly retooled to produce large numbers of a different kind of chip using the same production techniques as the line's prior output.

With the help of common components, we could construct a breadboard circuit just from this description. We need to take it a step further and create the layout, or patterns on the masks, in order to produce it on an IC manufacturing line. Transistors and wires that adhere to the circuit in the schematic are created by the rectangular forms in the layout, which is shown here as a stick diagram. Layout creation takes a lot of time, but it is crucial since the size of

the layout affects how much it will cost to construct a circuit as well as how quickly it will operate. In the production process, the layout patterns are transferred from the masks to the wafer using a photolithographic photographic printing technique. To modify the wafer just partially, the patterns the mask leaves behind are used: Impurities are introduced to the wafer at certain areas, insulating and A A' p-type transistor A A.

IP-Based Design, Fourth Edition, Modern VLSI Design Going Back to the Table of Contents On top of the wafer, conducting materials for digital systems and VLSI are also added. High temperatures, limited quantities of very poisonous chemicals, and ultra-clean surroundings are needed for these fabrication procedures. The wafer is split into a number of chips at the conclusion of processing. Manufacturing faults some of the chips on the wafer may not function since no manufacturing process is faultless. The smallest chip that can currently be reliably made is 1.5 to 2 cm on a side, whereas a wafer is in the range of 30 to 45 cm.

Because at least one flaw is nearly certain to occur on each wafer, wafers are chopped into smaller, functional chips. When the wafer is divided into chips, each chip is separately examined; those that pass the test are kept. The familiar to digital designer's packages include the functioning chips. Although the package body shields the chip from handling and the environment in some packages, in others, solder bumps directly link the chip to the packaging. In certain packages, small wires connect the chip to the package's pins [8].

A few different types of transistors and wires can be used to create all circuits, making integrated circuit manufacturing a potent technology. Additionally, any combination of transistors and wires can be built on a single fabrication line by simply changing the masks that determine the pattern of the components on the chip. Integrated circuits operate incredibly quickly because the circuits are relatively tiny. Moreover, we are not limited to creating just a few common chip kinds; we are free to create any function. We can create more complicated, quicker digital systems with the freedom provided by IC fabrication.A lot of work has been put into improving integrated circuit manufacturing because it has so much potential a large number of components can be produced using only a few common production techniques. The cost of developing a chip, however, rises as processors get more complicated and has a significant role in the final cost of the chip.

Moore's Law Gordon Moore anticipated that the number of transistors that could be produced on a chip would increase exponentially in the 1960s. His forecast, which is now referred to as Moore's Law, proved extremely accurate. The most important forecast made by Moore was that the number of transistors will double every two years. The International Technological Roadmap for Semiconductors (ITRS), which outlines methods to sustain Moore's Law's speed, is now maintained by an industry body. Charting the dates of the launch of significant goods that advanced the state of the manufacturing art demonstrates improvements in manufacturing capabilities. The black dots represent random-access memory, usually dynamic RAMs or DRAMs, while the squares represent different logic circuits, principally CPUs and digital signal processors (DSPs). Logic chips and memory chips both follow Moore's Law, with memory chips having more transistors per unit area at any given moment [9], [10].

Terminology The minimum channel length of a transistor is the most fundamental manufacturing process parameter. A technological node is a manufacturing innovation at a certain channel length. Micron, submicron, deep submicron, and now nanometer technologies are members of a family of technologies with comparable feature sizes that we often discuss. For technologies smaller than 100 nm, the phrase "nanometer technology" is often used.

#### CONCLUSION

VLSI (Very Large Scale Integration) technology has revolutionized the field of electronics and computing by allowing for the production of complex integrated circuits with millions or even billions of transistors on a single chip. VLSI technology has enabled the creation of smaller, faster, and more power-efficient devices that have transformed the way we live and work. The development of VLSI technology has been driven by continuous advances in semiconductor manufacturing processes, which have allowed for the fabrication of increasingly dense and complex integrated circuits. This has been accompanied by advances in design tools and techniques, which have enabled the creation of highly optimized and efficient designs.

#### REFERENCES

- [1] S. Tanaka and W. Kosonocky, "Welcome to the 2020 Symposia on VLSI Technology and Circuits," *IEEE Symposium on VLSI Circuits, Digest of Technical Papers.* 2020. doi: 10.1109/VLSICircuits18222.2020.9162814.

- [2] "2018 International Symposium on VLSI Technology, Systems and Application, VLSI-TSA 2018," 2018 International Symposium on VLSI Technology, Systems and Application, VLSI-TSA 2018. 2018.

- [3] M. LI and R. HUANG, "Device and integration technologies for VLSI in post-Moore era," *Sci. Sin. Informationis*, 2018, doi: 10.1360/n112018-00114.

- [4] R. D. Clark, "Emerging applications for high K materials in VLSI technology," *Materials*. 2014. doi: 10.3390/ma7042913.

- [5] D. L. Critchlow, "MOSFET Scaling-The Driver of VLSI Technology," *Proc. IEEE*, 1999, doi: 10.1109/JPROC.1999.752521.

- [6] S. Nicolay A., "Features of VLSI Components in Fully-depleted SOI CMOS Technology," *Nanoindustry Russ.*, 2018, doi: 10.22184/1993-8578.2018.82.46.48.

- [7] M. C. Martínez-Rodríguez, M. A. Prada-Delgado, P. Brox, and I. Baturone, "VLSI design of trusted virtual sensors," *Sensors (Switzerland)*, 2018, doi: 10.3390/s18020347.

- [8] "2019 Symposium on VLSI Technology, VLSI Technology 2019 Digest of Technical Papers," *Digest of Technical Papers Symposium on VLSI Technology*. 2019.

- [9] C. V. S. Chaitanya, C. Sundaresan, P. R. Venkateswaran, K. Prasad, and V. Siva Ramakrishna, "Design of high-speed multiplier architecture based on vedic mathematics," *Int. J. Eng. Technol.*, 2018, doi: 10.14419/ijet.v7i2.4.11228.

- [10] A. B. Kahng, L. Wang, and B. Xu, "TritonRoute: An initial detailed router for advanced VLSI technologies," in *IEEE/ACM International Conference on Computer-Aided Design, Digest of Technical Papers, ICCAD*, 2018. doi: 10.1145/3240765.3240766.

# **CHAPTER 2**

#### HARDWARE DEVELOPMENT OF VLSI

Dr. K Bhanu Rekha, Associate Professor Department of Electronics and Communication Engineering, Presidency University, Bangalore, India Email Id- bhanurekha@presidencyuniversity.in

#### **ABSTRACT:**

Hardware development of VLSI (Very Large Scale Integration) refers to the process of designing and fabricating integrated circuits that contain a large number of transistors and other electronic components on a single chip. VLSI technology has revolutionized the electronics industry by enabling the development of faster, smaller, and more complex electronic systems.

#### **KEYWORDS:**

Diamond Crystal, Electronic Components, Transistors, Hardware Development, Integrated Circuits.

#### **INTRODUCTION**

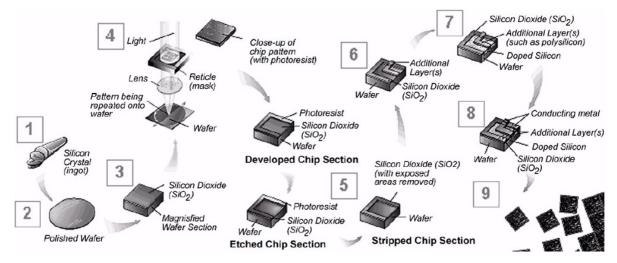

Pure silicon that has been melted at 1400 degrees Celsius is used in the wafer processing process. Thereafter, a small seed with the deemed essential crystal orientation is inserted into the liquid silicon and gradually removed at a pace of 1mm per minute. A cylindrical ingot is used to make the diamond crystal, which is subsequently separated into smaller ingots or platters before being polished and orientated.

- a) Photolithography: Both photographic and photo etching masks are used throughout this process. We next apply a photoresist layer on the wafer. A photo aligner is then used to align the wafer to a mask. The footprints that have made it through the mask are then shown when the wafer has been subjected to ultraviolet light.

- b) Etching: In this procedure, we degrade the surface of the wafer to produce patterns. We use more plasma liquid chemicals to remove the remaining photoresist while utilising an etching mask to safeguard the material's crucial regions [1].

Using a process called ion implantation, we introduce dopants into the semiconductor in order to produce the required electrical characteristic. The technique uses a beam of more dopant ions to precisely target certain areas of the wafer. The energy level of the beam determines how deeply the wafer is cut. Metallization: At this stage, a thin layer of aluminium is applied to the whole wafer.

Many hundred chips are included on each wafer for assembly and packaging. As a consequence, we use a diamond saw to cut the wafers into individual chips. These are subsequently put through electrical testing, and the unsuccessful ones are thrown away. Those that succeed, however, get a careful visual inspection under a microscope. The chosen chips that pass the visual inspection are next packed and scrutinised one more.

VLSI technology is ideally adapted to meet the needs of modern electronic devices and systems. Because to the growing need for functionality, reliability, performance, portability, and shrinking, VLSI innovation will continue to drive electronics progress [2]–[4].

For safety-critical real-time embedded systems (such satellite and surveillance systems), where dependability is equally as important as energy efficiency, reliability conscious energy management is necessary. Some early work has been done for the investigation of general system dependability for SoC. (system-on-a-chip). As part of the architecture level design of microprocessors, RAMP is the first instrument for modelling long-term processor reliability. In their subsequent published work, dynamic voltage, the authors proposed frequency scaling and the dynamic reliability management (DRM) paradigm. From a dependability perspective, these works of art showed that it wasn't sufficient to just manage the temperature or power.

The goal of many contemporary embedded system initiatives is to use less energy while maintaining the deadlines of all real-time job models. Power management techniques that leverage static or dynamic slack are currently being studied [5].

The reliability of a CPU will naturally rise with decreased power usage for the larger computer. Nevertheless, there is currently no single knob that can control the two objectives of increasing longevity and reducing power. Recent ideas for management jobs using low power techniques like DVFS include power with some dependability awareness. The bulk of presently available publications, however, focus on momentary flaws rather than wear-out failures over time. Recently, a method of work allocation and scheduling that takes dependability into account was proposed for non-linear, non-embedded processors [6], [7].

A semiconductor is placed on a Board using VLSI technology. It would not have been possible to make this Board using semiconductors without VLSI technology. Using state-of-the-art PCB To effectively perform the work while designing for the little margin of error available in VLSI technology, finite element analysis software is required. Allegro by Cadence is one such application that provides all the capabilities and analytical tools needed for both simple and intricate circuit designs [8], [9].

Comparison of architectural alternatives for a secret-key block encryption/decryption algorithm (AES cipher, block size 128 bit, key length 128 bit). The Rijndael algorithm makes extensive use of a so-called S-Box function and its inverse; the three hardware implementations include multiple look-up tables (LUTs) for implementing that function. Also, (de)ciphering and subkey preparation are carried out concurrently by separate hardware units. On that background, the throughput of the assembly language program running on a Pentium III is indeed impressive. This largely is because the Rijndael algorithm has been designed with the Pentium architecture in mind (MMX instructions, LUTs that fit into cache memory, etc.). Power dissipation remains daunting. Architecture General Purpose Special purpose Key component RISC Proc. CISC Proc.

#### DISCUSSION

Algorithms and hardware architectures are intimately related. While dedicated architectures outperform program-controlled processors by orders of magnitude in many applications of predominantly transformatorial nature, they cannot rival the agility and economy ofprocessor-type designs in others of more reactive nature. More precise criteria for finding out whether a dedicated architecture can be an option or not from a purely technical point of view puts various applications fromsignal and data processing into perspective.

Costs in hardware are not the same as those in software. As an example, permutations of bits within a data word are time-consuming operations in software as they must be carried out sequentially. In hardware, they reduce to simple wires that cross while running from one subcircuit to the next[10]. Look-up tables (LUTs) of almost arbitrary size, on the other hand, have become an abundant and cheap resource in any microcomputer while large on-chip

RAMs and ROMs tend to eat substantial proportions of the timing and area budgets of ASIC designs.

In an attempt to provide some guidance, we have collected ten criteria that an information processing algorithm should ideally meet in order to justify the design of a special-purpose VLSI architecture and to take full advantage of the technology. Of course, very few real-world algorithms satisfy all of the requirements listed. It is nevertheless safe to say that designing a dedicated architecture capable of outperforming a general-purpose processor on the grounds of performance and costs will prove difficult when too many of these criteria are violated. The list below begins with the most desirable characteristics and then follows their relative significance.

- 1. Loose coupling between major processing tasks. The overall data processing lends itself to being decomposed into tasks that interact in a simple and unmutable way. Whether those tasks are to be carried out consecutively or concurrently is of secondary importance at this point; what counts is to come up with a well-defined functional specification for each task and with manageable interaction between them. Architecture design, functional verification, optimization, and reuse otherwise become real nightmares.

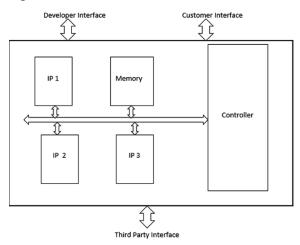

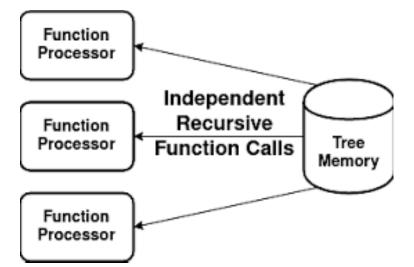

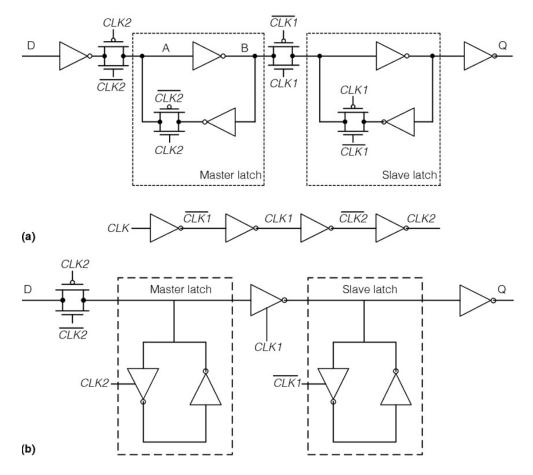

- 2. Simple control flow. The computation's control flow is simple. This key property can be tracked down to two more basic considerations: Figure 1 illustrate the specialization and model in VLSI.

Figure 1: illustrate the specialization and model in VLSI.

Exact meaning of operation and data item left unspecified; 16 bit-by-16 bit multiply– accumulate (MAC) operations on 16 bit samples are often considered typical in a context of digital signal processing).

- a) The course of operation does not depend too much on the data being processed; for each loop the number of iterations is a priori known and constant.

- b) The application does not ask for computations to be carried out with overly many varieties, modes of operations, data formats, distinct parameter settings, and the like.

The benefit of a simple control flow is twofold. For one thing, it is possible to anticipate the datapath resources required to meet a given performance goal and to design the chip's architecture accordingly. There is no need for statistical methods in estimating the computational burden or in sizing data memories and the like. For another thing, data path control can be put in different terms, the target algorithm is virtually free of branching and loops such as if...then [...else], while...do, and repeat...until that include data items in their condition clauses.

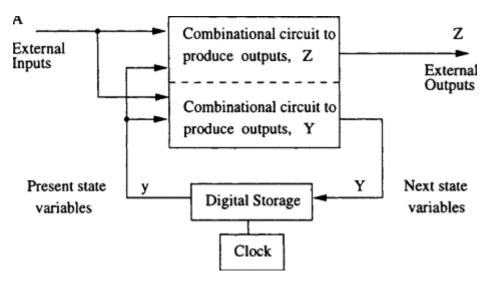

#### **Architectures of VLSI Circuits**

Handled by counters and by simple finite state machines (FSMs) that are small, fast, energyefficient and most important easy to verify. An overly complicated course of operations, on the other hand, that involves much datadependent branching, multitasking, and the like, favors a processor-type architecture that operates under control of stored microcode. Most control operations will then translate into a sequence of machine instructions that take several clock cycles to execute.

The flow of data is regular and their processing is based on a recurrence of a fairly small number of identical operations; there are no computationally expensive operations that are called only occasionally. Regularity opens a door for sharing hardware resources in an efficient way by applying techniques such as iterative decomposition and timesharing. Conversely, multiple data streams that are to be processed in a uniform way lend themselves to concurrent processing by parallel functional units. A regular data flow further helps to reduce communications overhead in terms of both area and interconnect delay as the various functional units can be made to exchange data over fixed local links. Last but not least, regularity facilitates reuse and reduces design and verification effort.

As opposed to this, operations that are used infrequently either will have to be decomposed into a series of substeps to be executed one after the other on a general-purpose datapath, which is slow, or will necessitate dedicated functional units bound to sit idle for most of the time, which inflates chip size. Irregular data flow requires long and flexible communication busses which are at the expense of layout density, operating speed, and energy efficiency.

Reasonable storage requirements. Overall storage requirements are modest and have a fixed upper bound.7 Memories that occupy an inordinate amount of chip area, say more than half or so, cannot be incorporated into ASICs in an economic way and must, therefore, be implemented off-chip from standard parts, see subsection. Massive storage requirements in conjunction with moderate computational burdens tend to place dedicated architectures at a disadvantage. Compatible with finite precision arithmetics. The algorithm is insensitive to effects from finite precision arithmetics. That is, there is no need for floating-point arithmetics; fairly small word widths of, say, 16 bit or less suffice for the individual computation steps. Standard microprocessors and DSPs come with datapaths of fixed and often generous width (24, 32, 64 bit, or even floating-point) at a given price. No extra costs arise unless the programmer has to resort to multiple precision arithmetics.

As opposed to this, ASICs and FPL offer an opportunity to tune the word widths of datapaths and on-chip memories to the local needs of computation. This is important because circuit size, logic delay, interconnect length, parasitic capacitances, and energy dissipation of addition, multiplication, and other operations all tend to grow with word width, combining into a burden that multiplies at an overproportional rate. Which precludes the use of dynamic data structures. 8 Processor datapaths tend to be fast and area effi cient because they are typically hand-optimized at the transistor level (e.g. dynamic logic) and implemented in tiled layout rather than built from standard cells. These are only rarely options for ASIC designers.

#### THE ARCHITECTURAL ANTIPODES

Nonrecursive linear time-invariant computation. The processing algorithm describes a nonrecursive linear time-invariant system over some algebraic field. Each of these properties opens a door to reorganizing the data processing in one way or another, see sections through for details. High throughputs, in particular, are much easier to obtain from nonrecursive computations as will become clear in section.

The algorithm does not make use of roots, logarithmic, exponential, or trigonometric functions, arbitrary coordinate conversions, translations between incompatible number systems, and other transcendental functions as these must either be stored in large look-up tables (LUT) or get calculated on-line in lengthy and often irregular computation sequences. Such functions can be implemented more economically provided that modest accuracy requirements allow approximation by way of lookups from tables of reasonable size, possibly followed by interpolation.

Extensive usage of data operations unavailable from standard instruction sets. Of course, there exist many processing algorithms that cannot do without costly arithmetic- logic operations. It is often possible to outperform traditional program-controlled processors in cases where such operations need to be assembled from multiple instructions. Dedicated datapaths can then be designed to do the same computation in a more efficient way. Examples include complex-valued arithmetics, add compare select operations, and many ciphering operations. It also helps when part of the arguments are constants because this makes it possible to apply some form of preprocessing. Multiplication by a variable is more onerous than by a constant, for instance. Throughput rather than latency is what matters. This is a crucial prerequisite for pipelined processing.

No divisions and multiplications on very wide data words. Multiplications involving wide arguments are not being used the algorithm does not make extensive use of multiplications and even less so of divisions as their VLSI implementation is much more expensive than that of addition/subtraction when the data words involved are wide. There is plenty of land between the architectural antipodes most markets ask for performance, agility, low power, and a modest design effort at the same time. In the face of such contradictory requirements, it is highly desirable to combine the throughput and the Recursiveness. Linear is meant to imply the principle of superposition  $f(x(t) + y(t)) \equiv f(x(t)) + f(y(t))$  and  $f(c x(t)) \equiv cf(x(t))$ . T im e-invariant means that the sole effect of delaying the input is a delay of the output by the same amount of time: if z(t) = f(x(t)) is the response to x(t) then z(t - T) is the response to x(t - T). Fields and other algebraic structures are compared. Dropping unit factors and/or zero sum terms (both at word and bit levels), substituting integer powers of 2 as arguments in multiplications and divisions, omitting insignificant contributions, special number representation schemes, taking advantage of symmetries, precomputed look-up tables, and distributed arithmetic, see subsection are just a few popular measures that may help to lower the computational burden in situations where parts of the arguments are known ahead of time.

#### **Architectures of VLSI Circuits**

Energy efficiency of a dedicated VLSI architecture for demanding but highly repetitive computations with the convenience and flexibility of an instruction set processor for more control-oriented tasks. This is because those parts of a system that ask for maximum computation rate are not normally those that are subject to change very often, and vice versa. The finding immediately suggests a setup where a software-controlled microcomputer cooperates with one or more dedicated hardware units. Separating the quest for computational efficiency from that for agility makes it possible to fully dedicate the various functional units to their respective tasks and to optimize them accordingly. Numerous configurations are possible and the role of the instruction set microcomputer varies accordingly.

Some digital systems and the computing requirements of major subfunctions thereof. Subfunctions primarily characterized by irregular control flow and/or repetitive control flow and Application need for flexibility need for comput. EfficiencyDVD player user interface, track seeking, 16-to-8 bit demodulation, tray and spindle control, error correction, processing of non-video data MPEG-2 decompression (directory, title, author, (discrete cosine transform), subtitles, region codes) video signal processing Cellular phone user interface, SMS, intermediate frequency directory management, filtering, (de)modulation, battery monitoring, channel (de)coding, communication protocol, error correction (de)coding, channel allocation, (de)ciphering, roaming, accounting speech (de)compression. Pattern recognition pattern classification, image stabilization, (e.g. as part of a object tracking, redundancy reduction, defensive missile) target acquisition, image segmentation, triggering of actions feature extraction[11].

#### CONCLUSION

Hardware development in VLSI technology has been critical to the creation of highly integrated and efficient electronic systems. The continued development of VLSI technology will play a significant role in the advancement of modern society and the growth of many industries. The hardware development in VLSI technology has led to the creation of a wide range of electronic devices, from microprocessors and memory chips to sensors and communication devices. It has also enabled the development of advanced systems such as autonomous vehicles, artificial intelligence, and the internet of things.

#### REFERENCE

- L. Louis, "Working Principle of Arduino and Using it as a Tool for Study and Research," *Int. J. Control. Autom. Commun. Syst.*, 2016, doi: 10.5121/ijcacs.2016.1203.

- [2] K. M. Cham, S. Y. Oh, and J. L. Moll, "Computer-Aided Design in VLSI Device Development," *IEEE J. Solid-State Circuits*, 1985, doi: 10.1109/JSSC.1985.1052335.

- [3] L. Louis, "Working Principle of a Arduino and Using It," *Int. J. Control. Autom. Commun. Syst.*, 2016.

- [4] M. Rudan, *Physics of Semiconductor Devices*. 2015. doi: 10.1007/978-1-4939-1151-6.

- [5] X. Chen, G. Liu, N. Xiong, Y. Su, and G. Chen, "A Survey of Swarm Intelligence Techniques in VLSI Routing Problems," *IEEE Access*, 2020, doi: 10.1109/ACCESS.2020.2971574.

- [6] J. Mostow and B. Balzer, "Application of a transformational software development methodology to VLSI design," *J. Syst. Softw.*, 1984, doi: 10.1016/0164-1212(84)90021-9.

- [7] S. T and J. R. M, "Survey on Power Optimization Techniques for Low PowerVLSI Circuitsin Deep Submicron Technology," *Int. J. VLSI Des. Commun. Syst.*, 2018, doi: 10.5121/vlsic.2018.9101.

- [8] M. C. Stamm, M. Wu, and K. J. R. Liu, "Information forensics: An overview of the first decade," *IEEE Access*, 2013, doi: 10.1109/ACCESS.2013.2260814.

- [9] M. A. Islam, P. K. Datta, and H. Myler, "VLSI structures for DNA sequencing—a survey," *Bioengineering*. 2020. doi: 10.3390/bioengineering7020049.

- [10] H. Chen, S. Saïghi, L. Buhry, and S. Renaud, "Real-time simulation of biologically realistic stochastic neurons in VLSI," *IEEE Trans. Neural Networks*, 2010, doi: 10.1109/TNN.2010.2049028.

- [11] T. Acharya and C. Chakrabarti, "A survey on lifting-based discrete wavelet transform architectures," J. VLSI Signal Process. Syst. Signal Image. Video Technol., 2006, doi: 10.1007/s11266-006-4191-3.

## **CHAPTER 3**

# ADVANCEMENTS IN PHYSICS-BASED EM MODELING: TECHNIQUES AND APPLICATIONS FOR CHARACTERIZING ELECTROMAGNETIC PHENOMENA

Dr. Manikandan M, Assistant Professor

Department of Electronics and Communication Engineering, Presidency University, Bangalore, India Email Id- manikandan.m@presidencyuniversity.in

#### **ABSTRACT:**

Electromagnetic (EM) modeling is a fundamental component of many fields, including electrical engineering, physics, and materials science. In particular, EM modeling is used to understand and predict the behavior of electromagnetic waves and fields in different materials and structures. Physics-based EM modeling is a technique that uses fundamental physical principles to describe the behavior of EM waves and fields, and it is often used to design and optimize complex devices and systems.

#### **KEYWORDS:**

Devices, Electrical Engineering, Electromagnetic Phenomena, Physics, EM waves.

#### **INTRODUCTION**

We look at some of the most recent advancements in EM modelling and evaluation techniques. We explain specifically on the EM thermodynamics, present malfunction patterns, and their limitations. In the next section, we look at the key Korhonen's nonlinear evolution equation for void production and void growth in the constrained region as well as the popular stress-based modelling of EM failures of metal wires used for connections. The most recent compact two-phase EM proposal models are provided here. The shortcomings of these three various EM models are then shown. First off, the recommended nucleation time formula, which according to the experiment's results should be near to, does not adequately forecast the current exponent. We suggest the four distinct EM frameworks, which address the problem by include "void nucleation," to minimize this.

We provide a clearer explanation of the terms "void growth phase" and "void incubation phase" and show how to use compact models to estimate the nucleation time and determine how long each of the three phases of nucleation, incubation, and failure last. Moreover, variations in wire resistance patterns may be predicted by the three-phase electromagnetic model, which is more in accordance with the information obtained from experiments. Moreover, we show how this study may be used to multi-segment connections using the rapid saturation volume estimation approach for connecting, which is crucial for determining the EM failure time to failure.

Electro migration (EM) is the term used to describe the directed movement of electrically charged particles. Owing to their momentum, copper (Cu) atoms migrate in the direction of the electrical field that is placed between them and the conducting electrons. Atoms move down the route, either with conducting lattice atoms or impurity electrons, towards the anode terminal of something like the metal wire. This coordinated atomic mobility at the cathode and a corresponding metal accumulation at the metal's anode end wire result in a decrease in metal density. The so-called diffuser barriers are holding the metal wires within, causing a depletion and growth of the metal volume since atoms can't just escape.[1]

Often, metallic objects are used to insert or contain Cu damascene linking wire barriers like Ta and are then covered with either a metallic or a dielectric layer. As a result, the wire volume changes as a result of atom depletion. Stress-Based EM and Stress Diffusion Modeling In addition to the Black and Blech formulations, which are based on a combination of semi-physics and physics, novel connecting wire has been developed employing electro migration phenomenon structures. First up in this part are the most sophisticated Korhonen's equation-based stress evolution-based EM models.

Next, we will show that the newly developed physics-based Cu damascene observed values are better consistent with the EM model by connecting the wires to the new three-phase EM model. The first time that the end of current-carrying strips was discovered was by Blech. The following motion is the Nernst-Einstein velocity, which is the drift speed for flow, where Fem is the EM-induced force caused by the electronic wind is the chemical diffusion coefficient and is computed using the formula  $Da = D0 \exp Ea$ , where D0 is the absorption coefficient the metal's flux.[2]

The electron wind-induced force (Fem) and the back-force brought on by changes in atom concentration (or stress gradients brought on by atoms being depleted somewhere at the cathode end and the atoms accumulating at the electrochemical end) are the two main forces acting on atoms during electromagnetic radiation (EM). Migration-induced buildup results in hydrostatic forces over the conductor, tightness at the anode, and torsion at the cathode end of the wire. The persistent, unidirectional stream flow both of these stresses, as well as the gradient of stresses along the metal line rise, actually act as a counterforce to reduce the metal corrosion caused by EM migration movement in some circumstances, even when a circuit is long or a significant signal is present.[3], [4] The basis of EM modeling is Maxwell's equations, which describe the behavior of electric and magnetic fields in the presence of charges and currents. These equations are fundamental to the understanding of EM waves and fields, and they provide a theoretical framework for predicting the behavior of EM phenomena in different materials and structures. Physics-based EM modeling involves using Maxwell's equations and other fundamental physical principles to develop models that accurately predict the behavior of EM waves and fields in a wide range of systems. There are several different methods used for physics-based EM modeling, including analytical techniques, numerical methods, and hybrid approaches that combine both analytical and numerical methods. In this article, we will review some of the most common methods used in physics-based EM modeling.

#### DISCUSSION

#### **Analytical Techniques**

Analytical techniques are used to develop closed-form solutions to Maxwell's equations for simple systems with known geometries and boundary conditions. These solutions can provide insights into the behavior of EM waves and fields in the system, and they can be used to develop simplified models that can be used for more complex systems [5] one of the most common analytical techniques used in EM modeling is the method of images. This technique involves using a mirrored image of a charged object to represent its effect on the EM field. The method of images can be used to solve a wide range of problems, including the calculation of the electric field around a charged plane, the capacitance of parallel plates, and the force between two charged particles. Another analytical technique used in EM modeling is the Green's function method. This technique involves using the Green's function of a system to find the solution to Maxwell's equations for an arbitrary source distribution. The Green's function is a mathematical function that describes the response of a system to a point

source, and it can be used to find the response to any source distribution using convolution. The Green's function method is commonly used in the study of scattering and diffraction phenomena, such as the behavior of electromagnetic waves in the presence of obstacles or discontinuities.

#### **Numerical Methods**

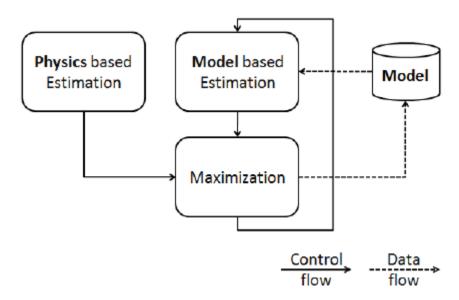

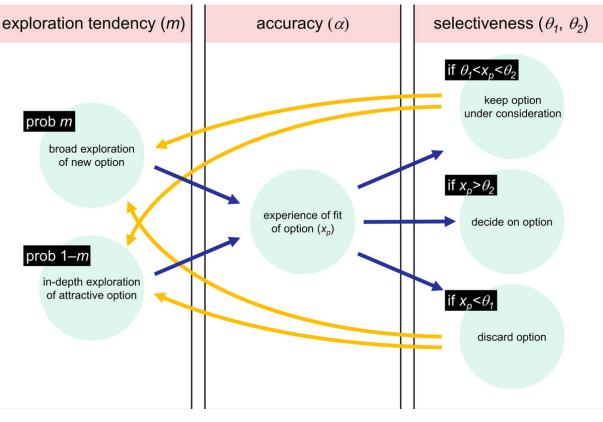

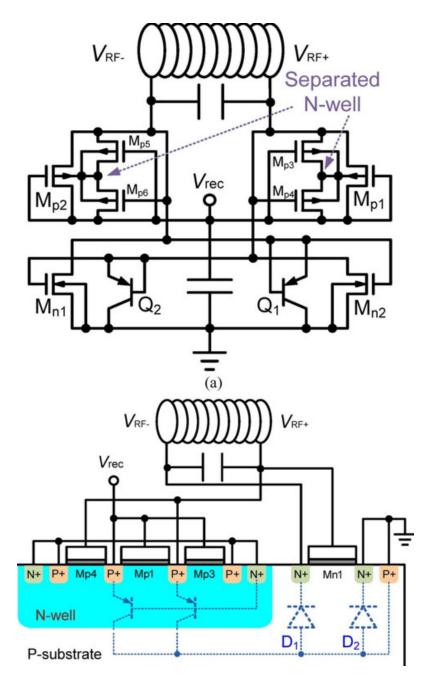

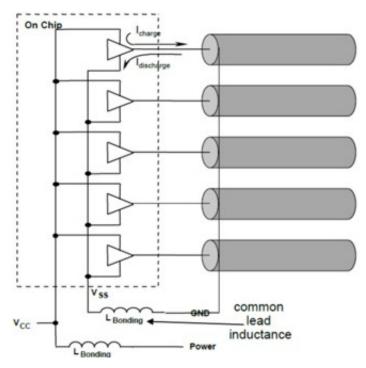

Numerical methods are used to develop solutions to Maxwell's equations for more complex systems that cannot be solved analytically. Numerical methods involve discretizing the system into a finite number of elements, such as cells or finite elements, and solving Maxwell's equations numerically for each element. This allows for the development of detailed and accurate models of the behavior of EM waves and fields in a wide range of systems. One of the most common numerical methods used in EM modeling is the finitedifference time-domain (FDTD) method. This method involves discretizing the system into a 3D grid of cells and solving Maxwell's equations for each cell at discrete time steps. The FDTD method is widely used in the study of complex systems, including the design of antennas, microwave circuits, and electromagnetic compatibility (EMC) issues. Another numerical method commonly used in EM modeling is the method of moments (MoM). The MoM involves discretizing the system into a set of surface or volume elements, and solving Maxwell's equations for each element using a set of integral equations. The MoM is commonly used in the study of antenna design, electromagnetic scattering, and other electromagnetic problems in which the geometry of the system is known[6], [7]. In three dedicated and one program-controlled processing units are arranged in a chain. Figure 1 illustrate the EM Algorithm starts with trajectory estimation based on the basic physics.

Figure 1: Illustrate the EM Algorithm starts with trajectory estimation based on the basic physics.

Each unit does its data processing job and passes the result to the downstream unit. While offering ample room for optimizing performance, this structure cannot accommodate much variation if everything is hardwired and tailor-made. Making the specialized hardware units support a limited degree of parametrization (e.g. wart data word width, filter order, code rate, data exchange protocol, and the like) renders the overall architecture more versatile while, at the same time, keeping the overhead in terms of circuit complexity and energy dissipation fairly low. The term weakly programmable satellites has been coined to reflect the idea. All

specialized hardware units now operate under control of a software-programmable host. A bidirectional bus gives the necessary liberty for transferring data and control words back and forth. Each coprocessor, or helper engine as it is sometimes called, has a rather limited repertoire of instructions that it can accept. It sits idle until it receives a set of input data along with a start command. As an alternative, the data may be kept in the host's own memory all the time but get accessed by the coprocessor via direct memory access (DMA). Once local computation has come to an end, the coprocessor sets a status flag and/or sends an interrupt signal to the host computer. The host then accepts the processed data and takes care of further action. Application-specific instruction set processors Patterning the overall architecture after a program-controlled processor affords much more flexibility. Application-specific features are largely confined to the data processing circuitry itself. That Architectures of VLSI Circuits is, one or more data paths are designed and hardwired so as to support specific data manipulations while operating under control of a common microprogram. The number of ALUs, their instruction sets, the data formats supported, the capacity of local storage, etc. are tailored to the computational problems to be solved. What's more, the various data paths can be made to operate simultaneously on different pieces of data, thereby providing a limited degree of concurrency. The resulting architecture is that of an application-specific instruction set processor (ASIP).

Application-specific instruction set processor (ASIP) (a), multiple cooperating ASIPs (b). The hardware organization of an ASIP bears much resemblance to architectural concepts from general-purpose computing. As more and more concurrent data path units are added, what results essentially is a very-long instruction word (VLIW) architecture. An open choice is that between a multiple-instruction multiple-data (MIMD) machine, where an individual field in the overall instruction word is set apart for each data path unit, and a single-instruction multiple-data (SIMD) model, where a bunch of identical data paths works under control of a single instruction word. Several data items can thus be made to undergo the same operation at the same time. In an effort to better serve high-throughput video and graphics applications, many vendors enhanced their microprocessor families in the late 1990s by adding special instructions that provide some degree of concurrency.

During each such instruction, the processor's data path gets split up into several smaller subunits. A data path of 64 bit can be made to process four 16 bit data words at a time, for instance, provided the operation is the While the mono-ASIP architecture of affords flexibility, it does not provide the same degree of concurrency and modularity as the multiple processing units. A multiprocessor system built from specialized ASIPs, therefore, an interesting extension. In addition, this approach facilitates the design, interfacing, reuse, test, and on-going update of the various building blocks involved. However, always keep in mind that defining a proprietary instruction set makes it impossible to take advantage of existing compilers, debugging aids, assembly language libraries, experienced programmers, and other resources that are routinely available for industry-standard processors. Industry provides us with such a vast selection of micro- and signal processors that only very particular requirements justify the design of a proprietary CPU.

Example While generally acknowledged to produce more realistic renderings of 3D scenes than industry standard raster graphics processors, ray tracing algorithms have long been out of reach for real-time applications due to the myriad floating-point computations and the immense memory bandwidth they require. Hardwired custom architectures do not qualify either as they cannot be programmed or as ray tracing necessitates many data-dependent recursions and decisions. Same for all of them. The technique is best described as sub-word parallelism, but is better known under various trademarks such as multimedia extensions (MMX), streaming SIMD extensions (SSE) (Pentium family), Velocity Engine, AltiVec, and VMX (PowerPC family). Reports on an interesting approach to expedite ASIP development whereby assembler, linker, simulator, and RTL synthesis code are generated automatically by system -level software tools. Product designers can thus essentially focus on defining the most appropriate instruction set for the processor in view of the target application.

#### **Architectures of VLSI Circuits**

Ray tracing may finally find more general adoption in multi-ASIP architectures that combine multiple ray processing units (RPUs) into one powerful rendering engine. Working under control of its own program thread, each RPU operates as a SIMD processor that follows a subset of all rays in a scene. The independence of light rays allows a welcome degree of scalability where frame rate can be traded against circuit complexity. The authors of [19] have further paid attention to defining an instruction set for their RPUs that is largely compatible with pre-existing industrial graphics processors.

#### **Configurable computing**

Another crossbreed between dedicated and general-purpose architectures did not become viable until the late 1990s but is now being promoted by FPL manufacturers and researchers The IEEE 1532 standard has also been created in this context. The idea is to reuse the same hardware for implementing sub functions that are mutually exclusive in time by reconfiguring FPL devices on the fly. As shown in fig.2.5, the general hardware arrangement bears some resemblance to the coprocessor approach of fig.2.3b, yet in-system configurable (ISC) devices are being used instead of hardwired logic. As a consequence, the course of operations is more sophisticated and requires special action from the hardware architects. For each major subtask, the architects must ask themselves whether the computations involved

- a) Qualify for being delegated to in-system configurable logic,

- b) Never occur at the same time or can wait until the FPL device becomes free, and

- c) Whether the time for having the FPL reconfigured in between is acceptable or not.

Typically this would be the case for repetitive computations that make use of sustained, highly parallel, and deeply pipelined bit-level operations. When designers have identified some suitable sub function, they devise a hardware architecture that solves the particular computational problem with the resources available in the target FPGA or CPLD, prepare a configuration file, and have that stored in a configuration memory. In some sense, they create a large hardware procedure instead of programming a software routine in the customary way. Whenever the host computer encounters a call to such a hardware procedure, it configures the FPL accordingly by downloading the pertaining configuration file. From now on, all the host has to do[8].

#### THE ARCHITECTURAL ANTIPODES

Is to feed the "new" coprocessor with input data and to wait until the computation is completed. The host then fetches the results before proceeding with the next subtask. It thus becomes possible to support an assortment of data processing algorithms each with itsoptimum architecture or almost so from a single hardware platform. What often penalizesthis approach in practice are the dead times incurred whenever a new configuration is being loaded. Another price to pay is the extra memory capacity for storing the configuration bits for all operationmodes. Probably the most valuable benefit, however, is the possibility of being able to upgrade information processing hardware to new standards and/or modes of operation even after the systemhas been fielded.

Examples Transcoding video streams in real time is a good candidate for reconfigurable computing because of the many formats in existence such as DV, AVI, MPEG-2, DivX, and H.264. For each conversion scheme, a configuration file is prepared and stored in local memory, from where it is transferred into the reconfigurable coprocessor on demand. And should a video format or variation emerge that was unknown or unpopular at the time when the system was being developed, extra configuration files can be made available in a remote repository from where they can be fetched much like software plug-ins get downloaded via the Internet. The results from a comparison between Lempel–Ziv data compression with a reconfigurable coprocessor and with software execution on a processor have been summarized. A related application was to circumvent the comparatively slow PCI bus in a PC.

#### **Extendable instruction set processors**

This latest and most exotic approach pioneered by Stretch borrows from ASIPs and from configurable computing. Both a program-controlled processor and electrically reconfigurable logic are present on a common hardware platform. The key innovation is a suite of proprietary EDA tools that allows system developers to focus on writing their application program in C or C++ as if for a regular general purpose processor. Those tools begin by profiling the software code in order to identify sequences of instructions that are executed many times over. For each such sequence, reconfigurable logic is then synthesized into a dedicated and massively parallel computation network that completes within one clock cycle ideally at least. Finally, each occurrence of the original computation sequence in the machine code gets replaced by a simple function call that activates the custom-made data path logic.

In essence, the base processor gets unburdened from lengthy code sequences by augmenting his instruction set with a few essential additions that fit the application and that get tailormade as an extension to the general procedure described here, an extra optimization step can be inserted before the coprocessor is configured. During this stage, the host would adapt a predefined generic configuration to take advantage of particular conditions of the specific situation at hand. Consider pattern recognition, for instance, where the template remains unchanged for a prolonged lapse of time, or secret-key (de)ciphering, where the same holds true for the key. As stated item 1, it is often possible to simplify arithmetic and almost on the fly. Yet, the existence of reconfigurable logic and the business of coming up with a suitable hardware architecture are hidden from the system developer. The fact that overall program execution remains strictly sequential should further simplify the design process.

#### Digest

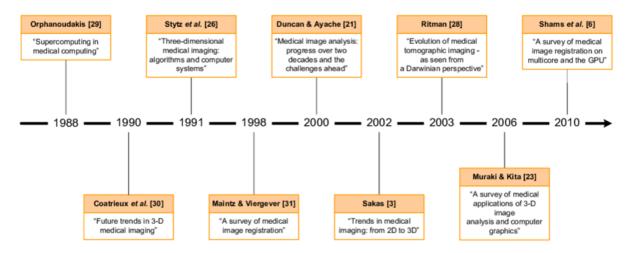

Program execution on a general-purpose processor and hardwired circuitry optimized for one specific flow of computation are two architectural antipodes. Luckily, many useful compromises exist in between, and this is reflected. A general piece of advice is this: Rely on dedicated hardware only for those sub functions that are called many times and are unlikely to change; keep the rest programmable via software, via reconfiguration, or both. The architectural solution space viewed as a globe. While there are many ways to trade agility for computational efficiency and vice versa, the two seem to be mutually exclusive as we know of no architecture that would meet both goals at the same time. Their conceptual differences notwithstanding, many techniques for obtaining high performance at low cost are the same for general- and special-purpose architectures.